**Федеральный исследовательский центр «Информатика и управление»

Российской Академии Наук (ФИЦ ИУ РАН)**

На правах рукописи

**Хилько Дмитрий Владимирович**

**ИССЛЕДОВАНИЕ И РАЗРАБОТКА ПОТОКОВОЙ РЕКУРРЕНТНОЙ

АРХИТЕКТУРЫ ДЛЯ ЭФФЕКТИВНОЙ РЕАЛИЗАЦИИ ПАРАЛЛЕЛИЗМА

В ОБЛАСТИ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ**

2.3.2 «Вычислительные системы и их элементы»

Диссертация на соискание ученой степени

кандидата технических наук

Научный руководитель

к.т.н., ведущий научный сотрудник

Степченков Юрий Афанасьевич

Москва – 2023

## Оглавление

|                                                                                    |    |

|------------------------------------------------------------------------------------|----|

| Введение.....                                                                      | 5  |

| Глава 1 Исследование потоковой рекуррентной архитектуры и ее прототипа ГАРОС ..... | 14 |

| 1.1 Параллельные вычислительные системы .....                                      | 14 |

| 1.1.1 Классификация параллельных архитектур Кришнамарфи .....                      | 15 |

| 1.1.2 Способы организации параллельных вычислений .....                            | 16 |

| 1.2 Анализ потоковой модели вычислений и проблем ее реализации .....               | 21 |

| 1.2.1 Принципы потоковой модели вычислений .....                                   | 21 |

| 1.2.2 Структурные элементы потоковой модели вычислений .....                       | 22 |

| 1.2.3 Характерные проблемы реализации потоковых архитектур.....                    | 25 |

| 1.2.4 Реализация структур данных в потоковых архитектурах.....                     | 28 |

| 1.2.5 Балансировка вычислительной нагрузки .....                                   | 32 |

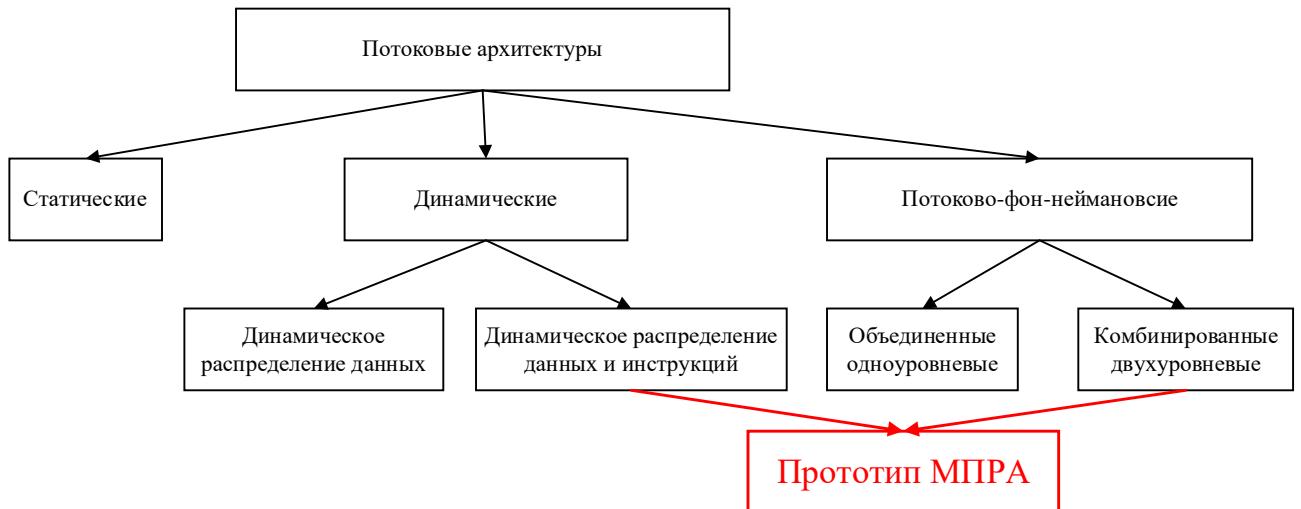

| 1.2.6 Комбинированные потоково-фон-неймановские архитектуры.....                   | 33 |

| 1.2.7 Позиционирование МПРА в классификации потоковых архитектур .....             | 36 |

| 1.3 Концептуальные основы многоядерной потоковой рекуррентной архитектуры .....    | 36 |

| 1.3.1 Рекуррентно-потоковая модель вычислений и архитектура на ее основе .....     | 36 |

| 1.3.2 Высокоуровневый прототип МПРА .....                                          | 41 |

| 1.3.3 Модель программирования МПРА .....                                           | 45 |

| 1.3.4 Анализ функциональных возможностей отдельных блоков прототипа МПРА .....     | 52 |

| 1.4 Отечественные вычислительные системы на основе потоковой архитектуры .....     | 60 |

| 1.4.1 Многоклеточная архитектура «Мультиклет» .....                                | 60 |

| 1.4.2 Параллельная потоковая вычислительная система «Буран».....                   | 63 |

| 1.5 Сравнительный анализ ГАРОС, Мультиклет и ППВС Буран .....                      | 65 |

| 1.6 Выводы к главе 1. Постановка задачи исследования .....                         | 66 |

| Глава 2 Разработка прототипа МПРА для задач цифровой обработки сигналов .....      | 69 |

| 2.1 Анализ проблем реализации задач ЦОС в существующей версии прототипа МПРА ..... | 69 |

| 2.2 Развитие микроархитектуры Вычислителей .....                                   | 72 |

| 2.2.1 Структура усовершенствованного МАС-блока.....                                | 72 |

|                                                                                              |     |

|----------------------------------------------------------------------------------------------|-----|

| 2.2.2 Развитие системы команд .....                                                          | 75  |

| 2.2.3 Методы поддержки многозадачности .....                                                 | 75  |

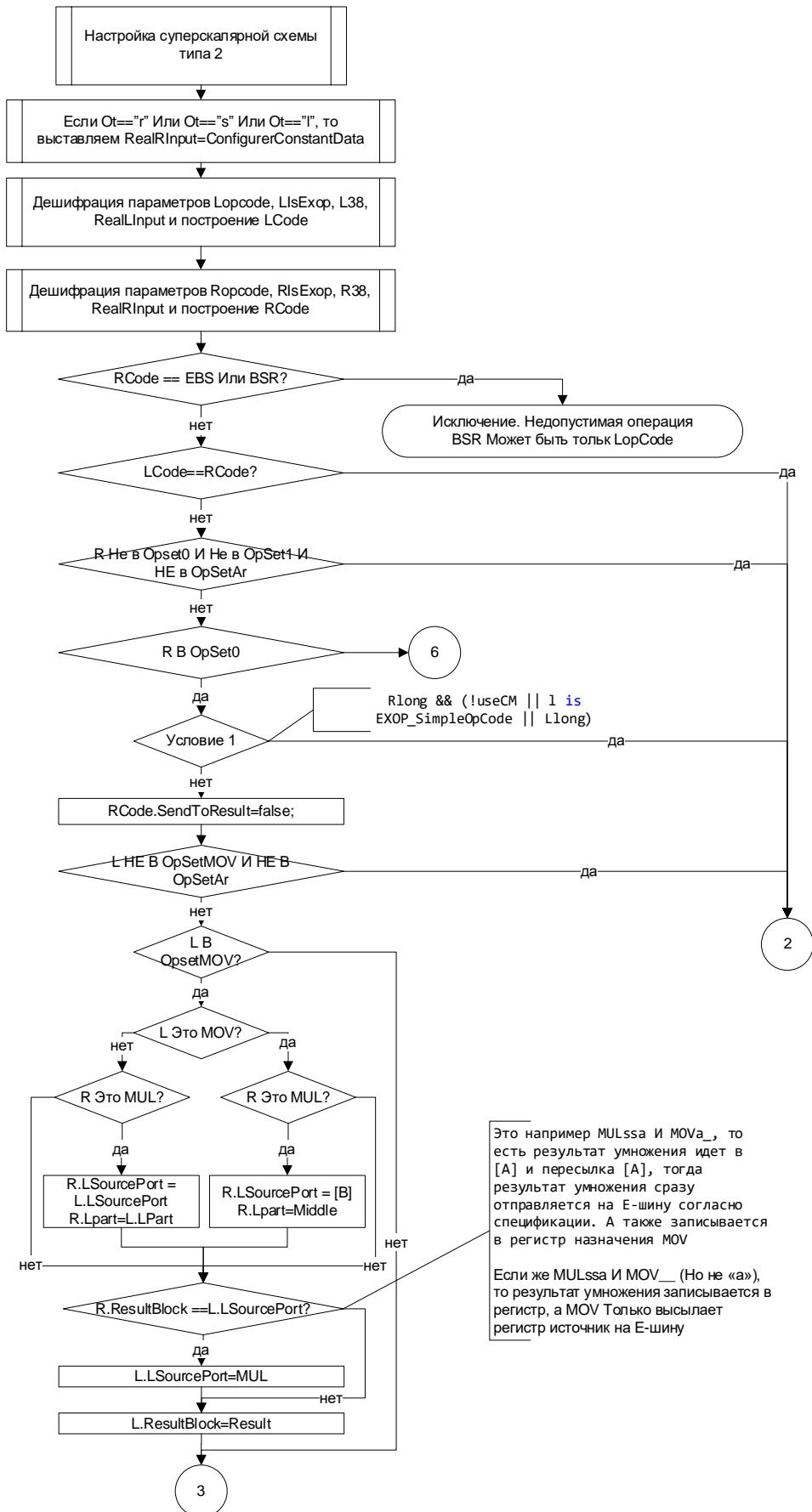

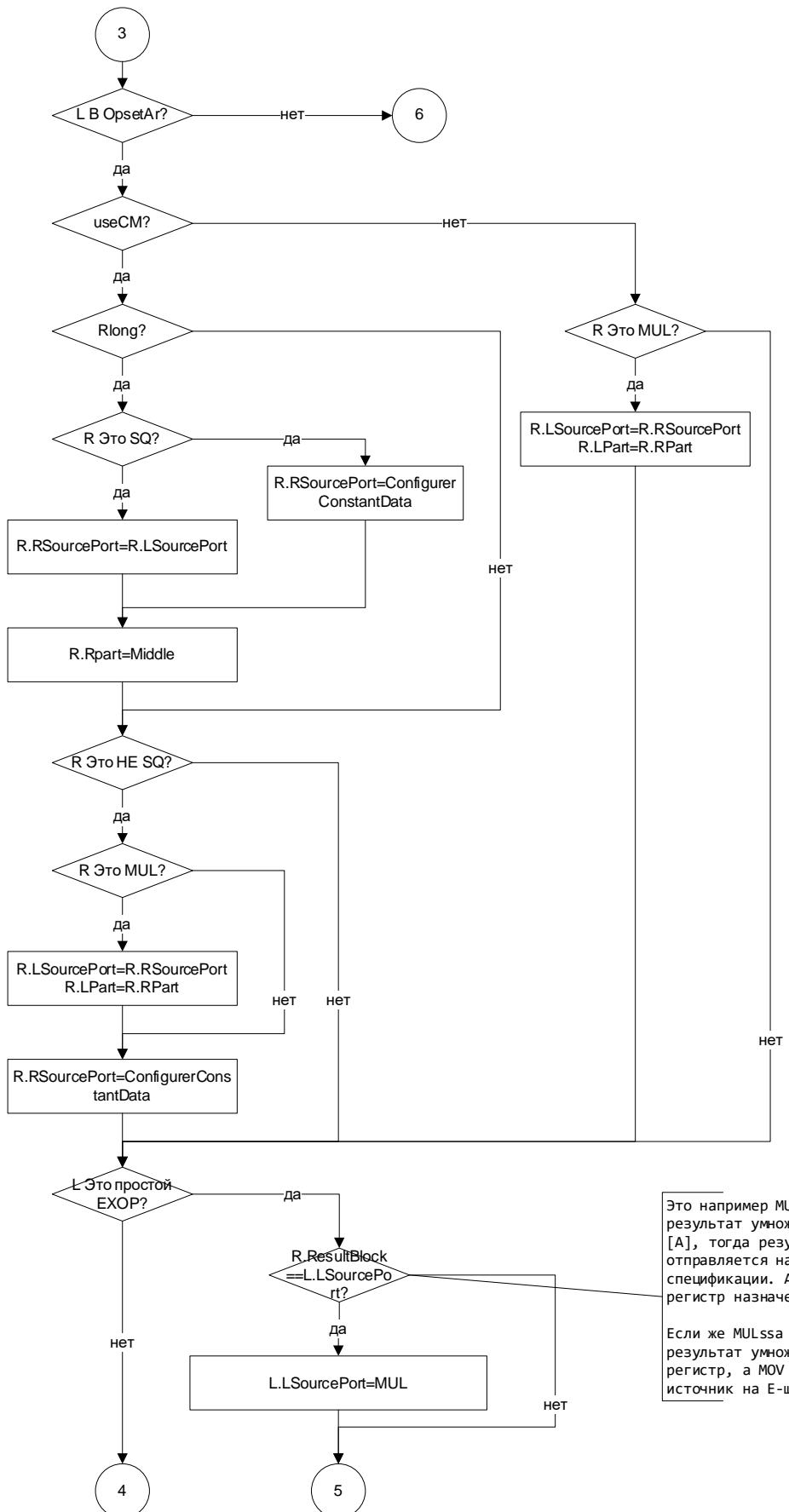

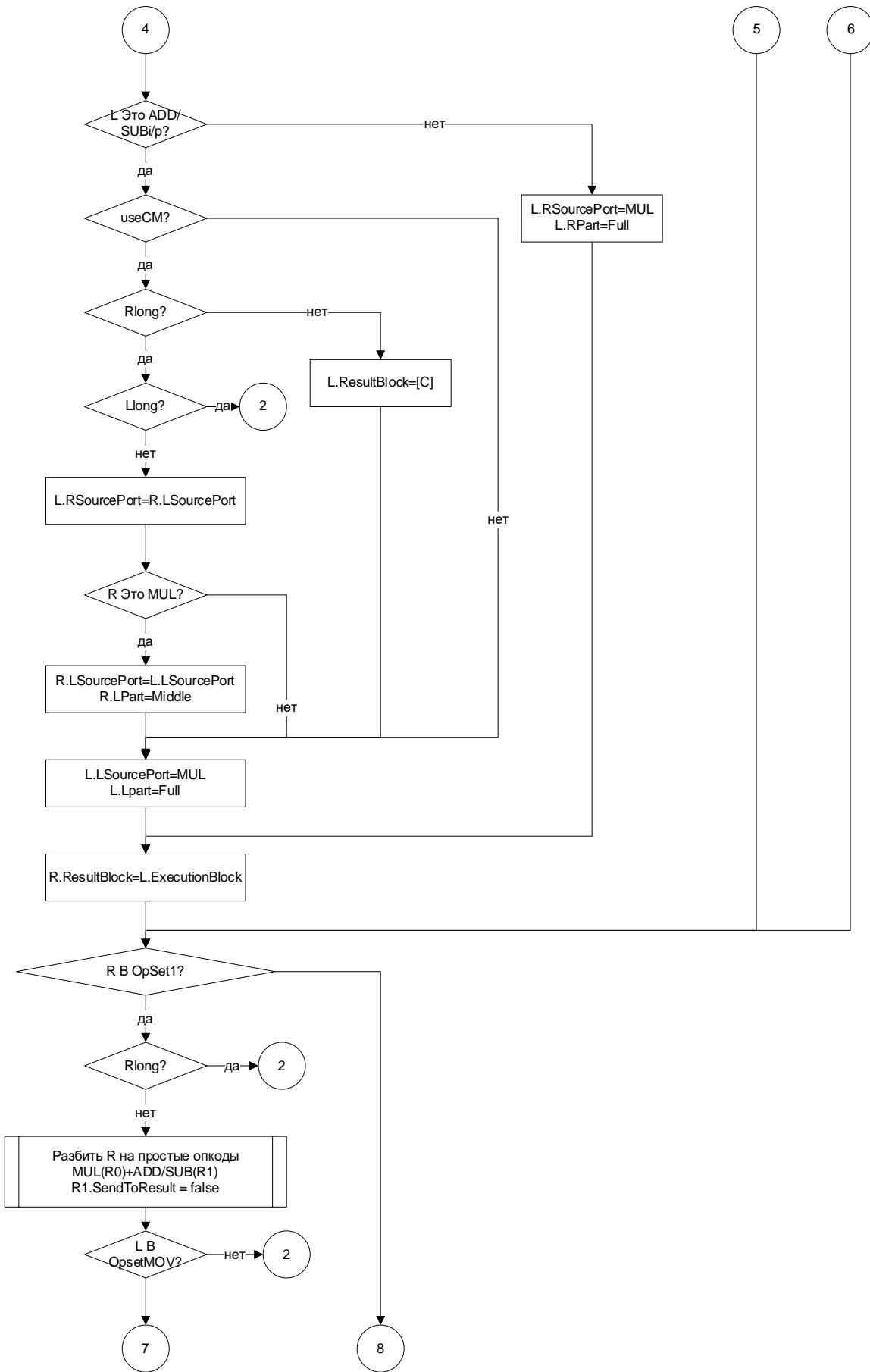

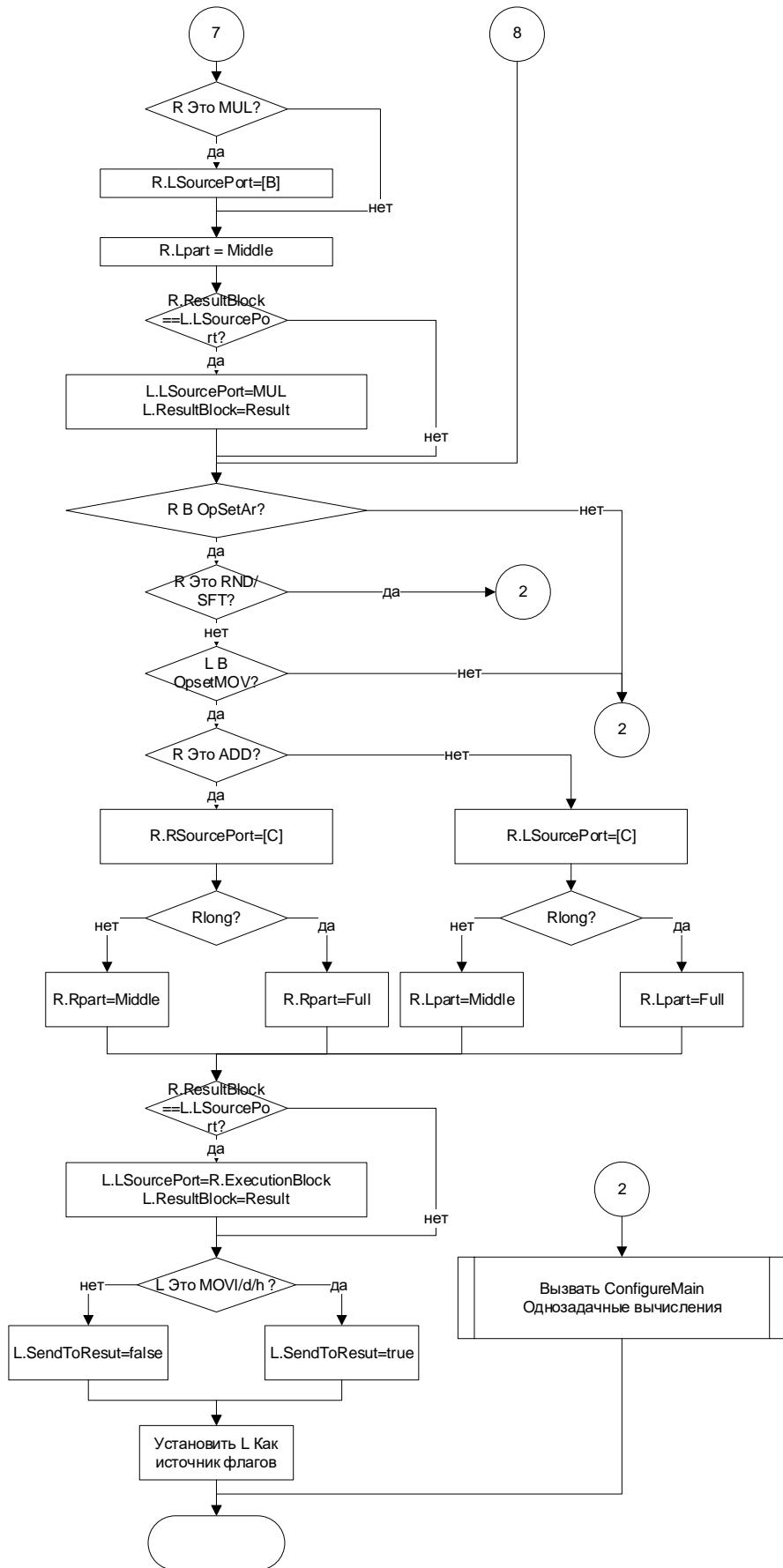

| 2.2.4 Алгоритмы функционирования усовершенствованного Вычислителя .....                      | 78  |

| 2.3 Память констант подгружаемая .....                                                       | 80  |

| 2.4 Многократное исполнение капсул .....                                                     | 82  |

| 2.5 Механизм косвенной репликации .....                                                      | 83  |

| 2.6 Обработка выходных данных .....                                                          | 84  |

| 2.7 Аппаратная поддержка алгоритма БПФ .....                                                 | 87  |

| 2.7.1 Описание алгоритмов ДПФ и БПФ .....                                                    | 88  |

| 2.7.2 Анализ существующих реализаций БПФ .....                                               | 90  |

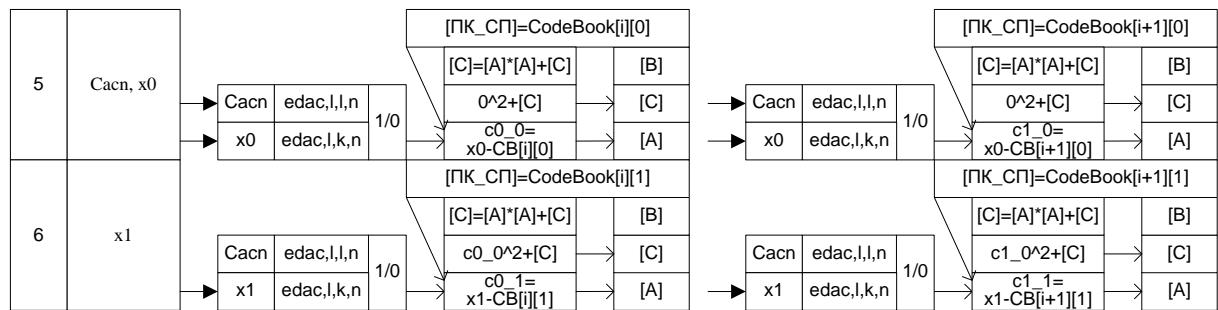

| 2.7.3 Модифицированные средства аппаратной поддержки БПФ .....                               | 96  |

| 2.8 Выводы к главе 2 .....                                                                   | 101 |

| Глава 3 Разработка отдельных элементов методологии программирования и отладки ГАРОС.         | 103 |

| 3.1 Развитие модели программирования ГАРОС .....                                             | 103 |

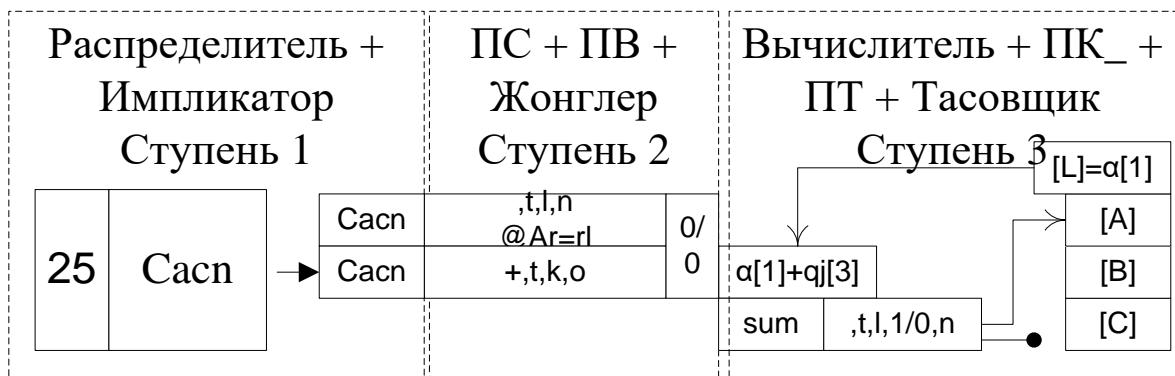

| 3.2 Элементы методологии программирования ГАРОС .....                                        | 104 |

| 3.3 Инструменты моделирования ГАРОС .....                                                    | 110 |

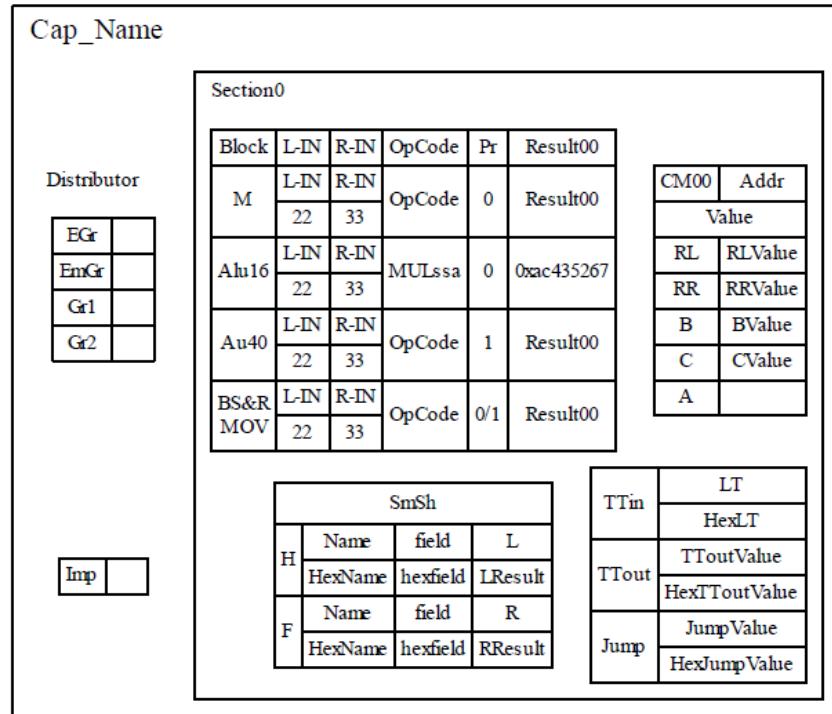

| 3.3.1 Программная имитационная модель .....                                                  | 110 |

| 3.3.2 Аппаратная VHDL-модель .....                                                           | 116 |

| 3.4 Средства аппаратно-программного моделирования и отладки .....                            | 118 |

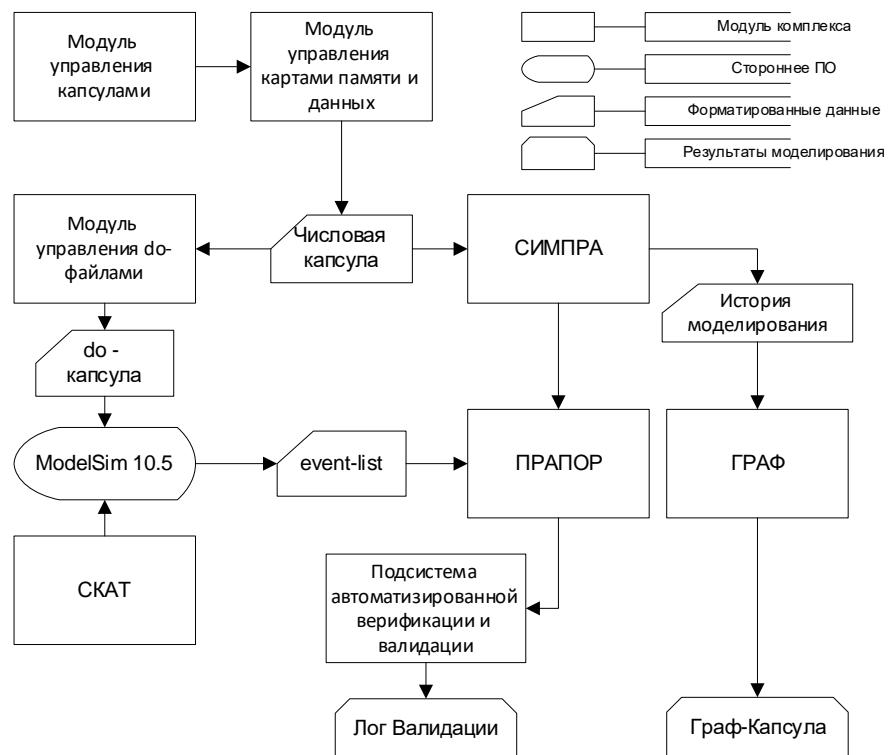

| 3.4.1 Программный комплекс моделирования потоковой многоядерной вычислительной системы ..... | 118 |

| 3.4.2 Подсистема имитационного моделирования СИМПРА .....                                    | 120 |

| 3.4.3 Подсистема аппаратного моделирования СКАТ .....                                        | 122 |

| 3.4.4 Подсистема автоматизированного построения граф-капсул ГРАФ .....                       | 123 |

| 3.4.5 Подсистема автоматизированной верификации и валидации ГАРОС .....                      | 126 |

| 3.5 Выводы к главе 3 .....                                                                   | 129 |

| Глава 4 Результаты программных и аппаратных испытаний ГАРОС .....                            | 130 |

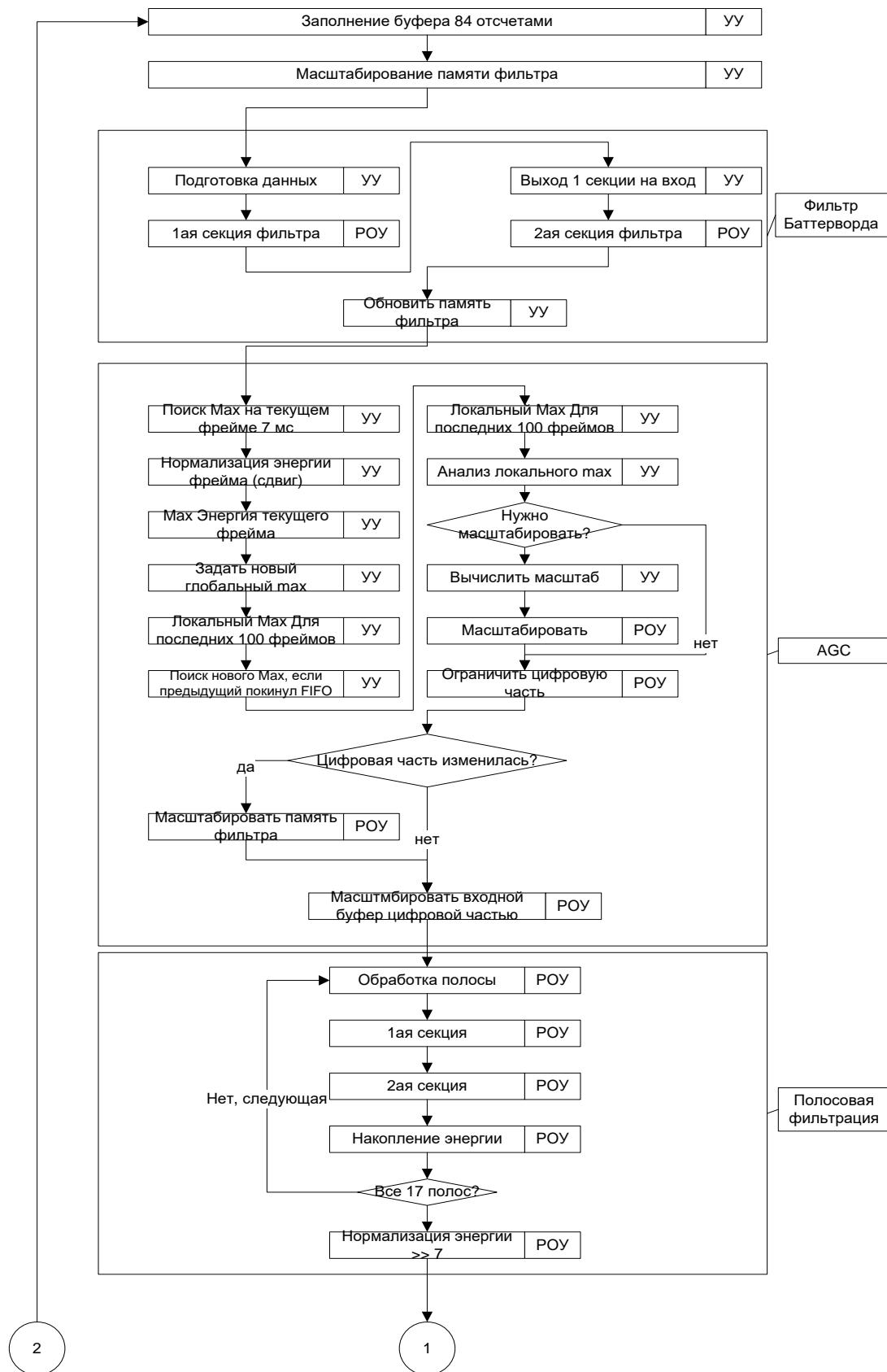

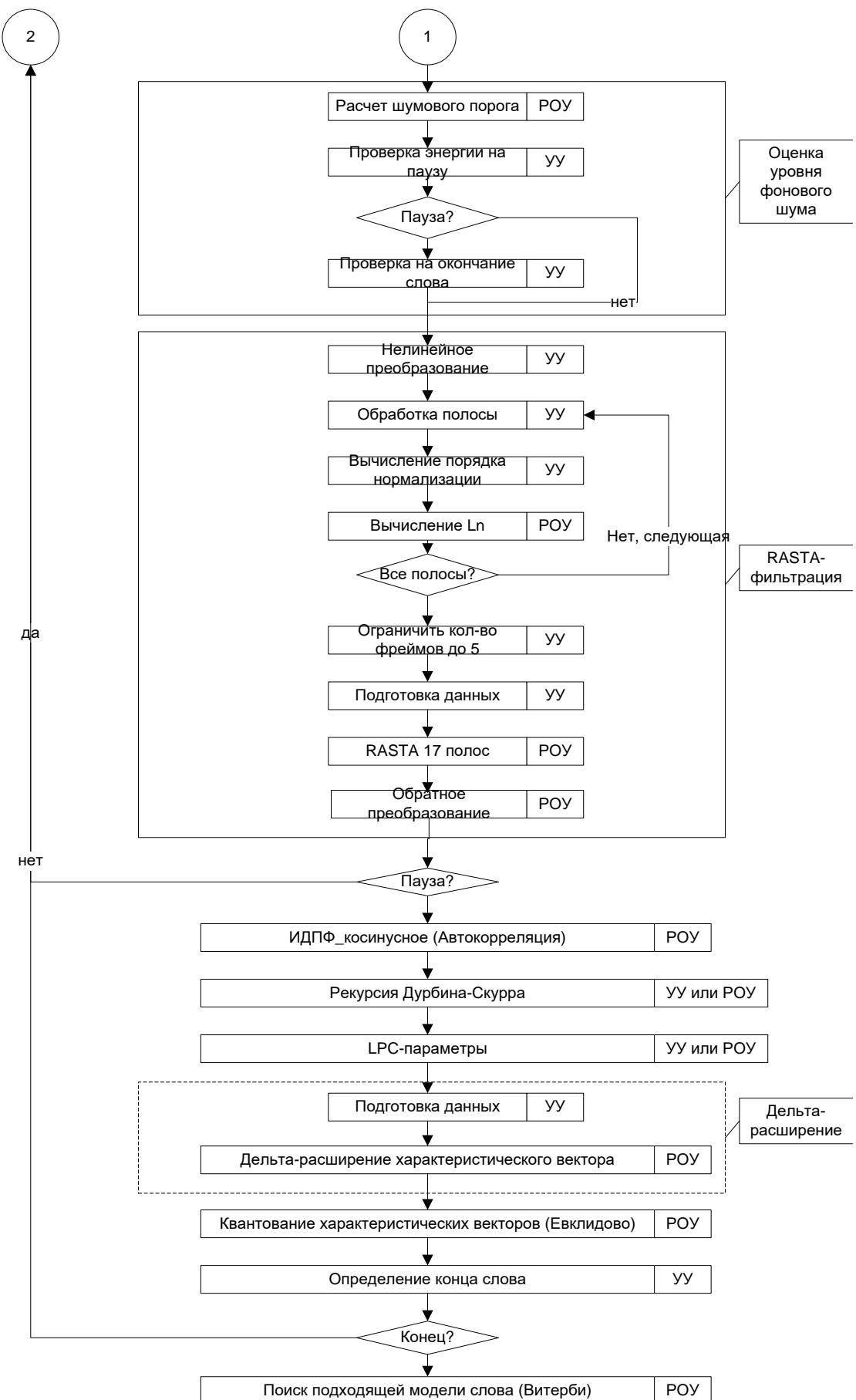

| 4.1 Постановка демонстрационной задачи РИС .....                                             | 130 |

| 4.2 Результаты применения методики программирования для РИС .....                            | 131 |

|                                                                                |     |

|--------------------------------------------------------------------------------|-----|

| 4.3 Результаты программно-аппаратных испытания РИС на моделях .....            | 136 |

| 4.4 Результаты испытаний РИС на ПЛИС прототипе архитектуры .....               | 137 |

| 4.5 Оценка производительности ГАРОС на комплекте бенчмарков BDTIMark2000 ..... | 139 |

| 4.6 Выводы к главе 4 .....                                                     | 141 |

| Заключение .....                                                               | 142 |

| Список сокращений и условных обозначений .....                                 | 145 |

| Список литературы .....                                                        | 146 |

| Приложение А .....                                                             | 157 |

## Введение

### Актуальность исследования

Одна из ключевых характеристик любой вычислительной системы – это ее производительность. На сегодняшний день большинство вычислительных систем основаны на традиционной архитектуре, предложенной фон-Нейманом. Долгое время высокого показателя производительности фон-Неймановских систем удавалось достигать путем повышения тактовой частоты. Но уже на уровне частот 3-4 ГГц проблемы питания и охлаждения процессора становятся определяющими. Поэтому ведутся исследования в области разработки высокопроизводительных архитектур вычислительных систем. Одним из основных способов повышения производительности является реализация параллельных вычислений на различных уровнях: команд, данных и задач.

Современные фон-Неймановские процессоры реализуют широкий набор средств реализации параллелизма уровня команд, а также состоят из множества вычислительных ядер. Однако, в основе традиционной архитектуры лежит последовательный вычислительный процесс, что приводит к высокой аппаратной избыточности механизмов реализации параллелизма. Это привело к необходимости разработки новых нетрадиционных архитектур вычислительных систем. Наиболее перспективной нетрадиционной архитектурой является потоковая архитектура, в которой поток данных имеет приоритет над потоком команд и является инициатором вычислений. Вычислительные системы, функционирующие под управлением потока данных, теоретически могут обеспечить большую производительность параллельных вычислений по сравнению с фон-неймановскими. Связано это с отсутствием «узких мест», характерных для фон-неймановской архитектуры, а также исключением вероятности обработки неподготовленных данных.

Исследование и разработка систем потоковой модели вычислений и архитектуры является актуальной задачей начиная с 1980-х годов и по настоящее время. Тем не менее, исследователи столкнулись с целым рядом проблем, которые не позволили построить эффективные вычислительные системы на основе потоковой архитектуры. К данным проблемам относятся: реализация рекурсии, реализация циклов, обработка константных данных, высокая степень избыточности тегированных данных, сложность и дороговизна аппаратной реализации механизмов сравнения тегированных данных, неэффективность при вычислении последовательных фрагментов алгоритмов и др. Поэтому данный класс систем не получил широкого распространения.

В поисках путей усовершенствования потоковой модели вычислений коллективом Института кибернетики имени В. М. Глушкова НАН Украины (Палагин А.В., Яковлев Ю.С. Махиборода А.В, и др.) была предложена идея новой потоковой модели вычислений, которая

впоследствии была развита и доработана сотрудниками ИПИ РАН (в настоящее время ФИЦ ИУ РАН) – Степченковым Ю.А., Филином А.В., Петрухиным В.С. и др. Данная модель вычислений была названа рекуррентно-потоковой.

Другой группой российских исследователей потоковой модели вычислений был коллектив ИПИ РАН под руководством академика Бурцева В.С. (Стемпковский А.Л., Хайлова И.К., Твердохлебов М.В. и др.). После кончины академика Бурцева большая часть коллектива перешла в ИППМ РАН. К настоящему времени коллектив под руководством Стемпковского А.Л. получил несколько грантов для исследования этой проблематики и занимается разработкой параллельной потоковой вычислительной системы «Буран» (ППВС «Буран»). «Буран» является системой массового параллелизма и реализует мелкозернистый параллелизм.

Наиболее коммерчески успешной отечественной архитектурой, основанной на использовании принципов потоковой модели вычислений, является Мультиклеточная архитектура. Данный проект начал свое развитие в 2001 году и к 2013 году успел получить несколько дипломов и наград. Процессоры на основе данной архитектуры позиционируются как отказоустойчивые. Основным принципом функционирования является широковещательная рассылка исполняемой программы и данных каждому вычислительному ядру процессора. Таким способом достигается использование естественного параллелизма, внеочередного исполнения команд и реализация мелкозернистого параллелизма.

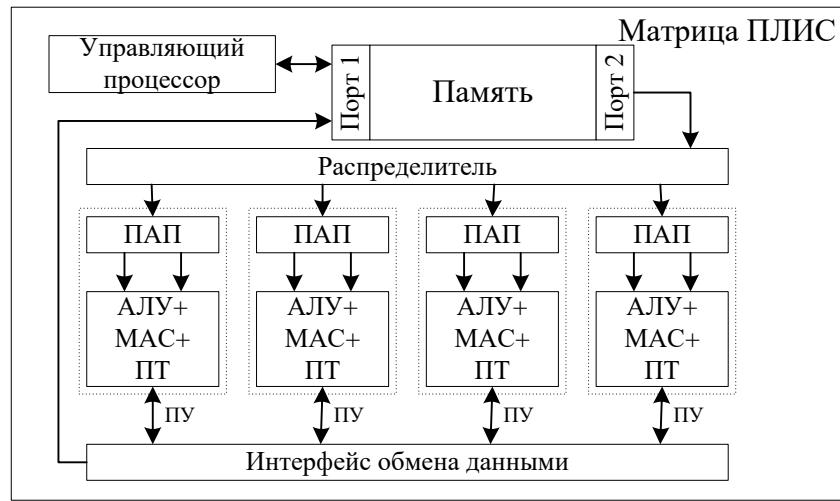

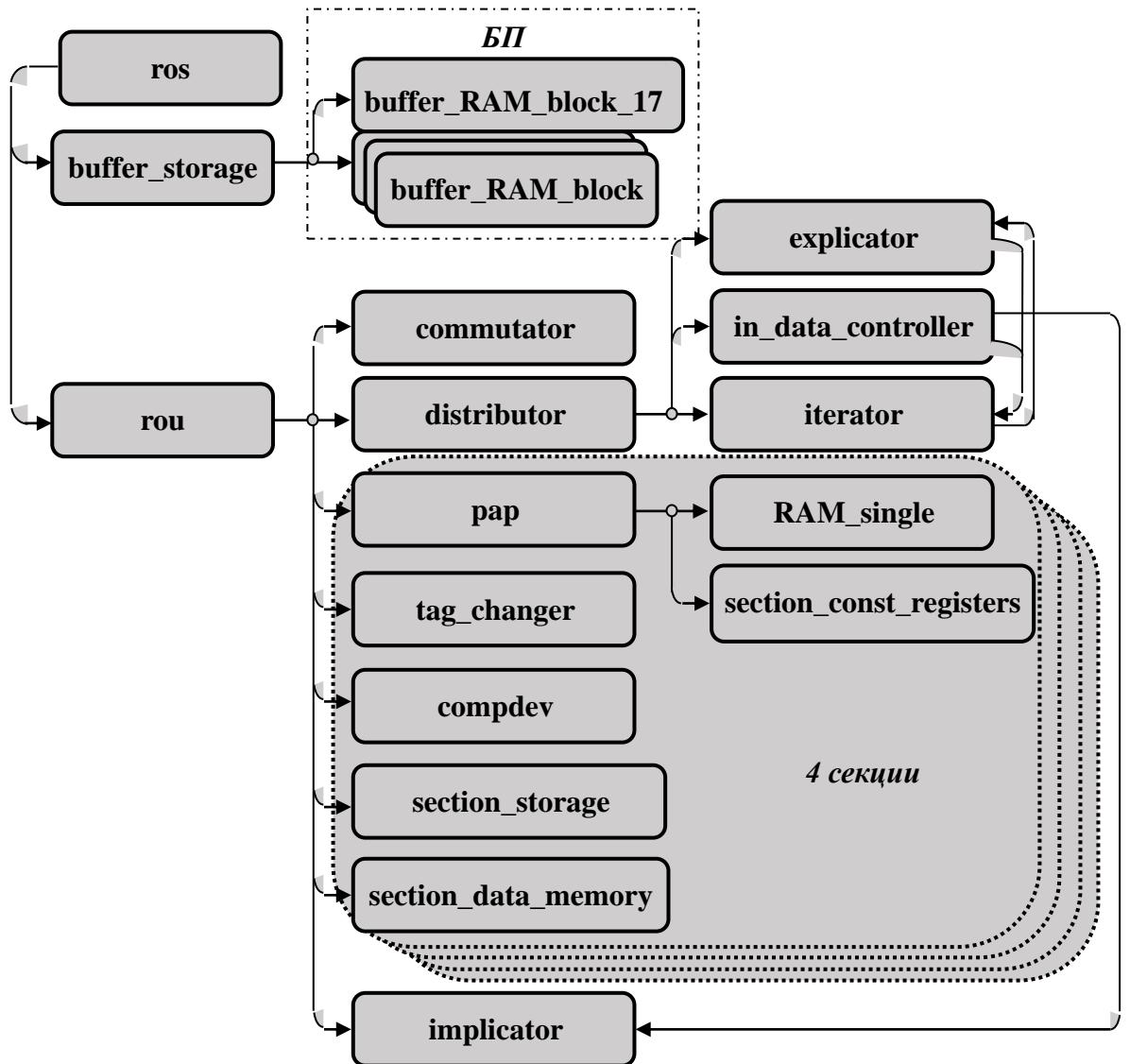

На базе рекуррентно-потоковой модели в ФИЦ ИУ РАН ведутся работы по созданию нетрадиционной рекуррентной архитектуры, предназначеннной для реализации параллельных вычислений ограниченной размерности в области цифровой обработки сигналов (ЦОС). Новая архитектура названа многоядерной потоковой рекуррентной архитектурой (МПРА). В настоящей реализации это гибридная двухуровневая архитектура рекуррентного обработчика сигналов (ГАРОС) с традиционным процессором на верхнем (управляющем) уровне и рекуррентным операционным устройством (РОУ) на нижнем уровне. В состав РОУ входят четыре вычислительных ядра.

В ФИЦ ИУ РАН также разработана идеология и методология проектирования самосинхронных схем, правильное функционирование которых не зависит от задержек составляющих их элементов. Данные схемы и системы на их основе обладают рядом свойств, выделяющих их из общего ряда цифровых устройств. Они «естественно надежны», поскольку гарантируют сохранение работоспособности аппаратуры в широком диапазоне дестабилизирующих факторов. Самосинхронизация на логическом уровне (по готовности данных в потоковой модели) хорошо сочетается с самосинхронизацией на аппаратном уровне (по готовности результата). Поэтому реализация МПРА также ориентирована на самосинхронный базис.

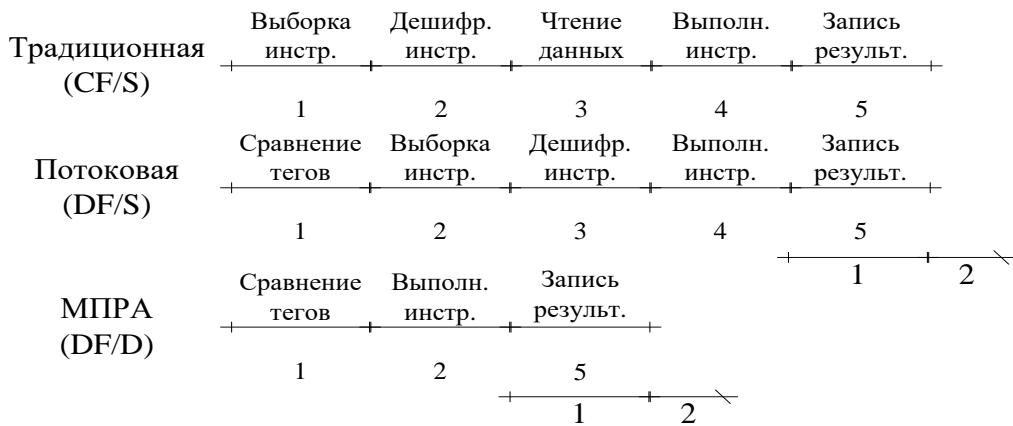

В основе рекуррентно-потоковой модели лежат принципы самодостаточных данных и рекуррентности. Самодостаточность данных заключается в организации единого потока данных и инструкций. Каждый элемент единого потока (операнд) образует исполняемый пакет, который спускается на исполнение в свободное ядро РОУ. Наличие в пакете и инструкций и данных упраздняет необходимость адресации памяти программ и памяти данных в привычном понимании. Необходимость адресации остается на уровне выше для корректного формирования исполняемых пакетов и их рассылки по вычислительным ресурсам. Это позволяет исключить этапы выборки данных и инструкций и совместить этап дешифрации инструкции с этапом ее выполнения. В результате общее количество этапов обработки пакета снижается практически вдвое ценой относительно небольшого увеличения его размера.

Одной из ключевых проблем потоковой модели вычислений является высокая степень избыточности тегированных данных. В некоторых случаях объем теговой информации может в разы превышать объем данных, которым эта информации принадлежит. Для решения этой проблемы в рекуррентно-потоковой модели вычислений предложен принцип рекуррентности. Данный принцип заключается в вычислении каждой следующей инструкции в ходе развития вычислительного процесса как функции от текущей исполняемой инструкции. В процессе вычислений происходит порождение новых исполняемых пакетов (рекуррентная развертка), которые отправляются на дальнейшую обработку. Следовательно, исходный поток инструкций рекуррентно сворачивается (сжимается), что позволяет резко сократить накладные расходы, связанные с опережающим хранением трассы вычислительного процесса. Сжатие также позволяет упростить описание и хранение вычислительного контекста. В результате реализации принципа рекуррентности общая избыточность теговой информации значительно снижается.

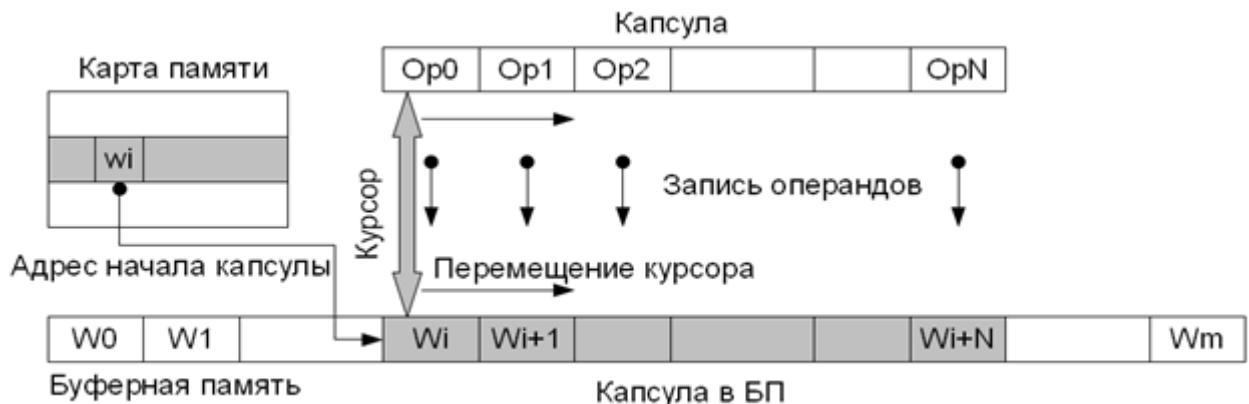

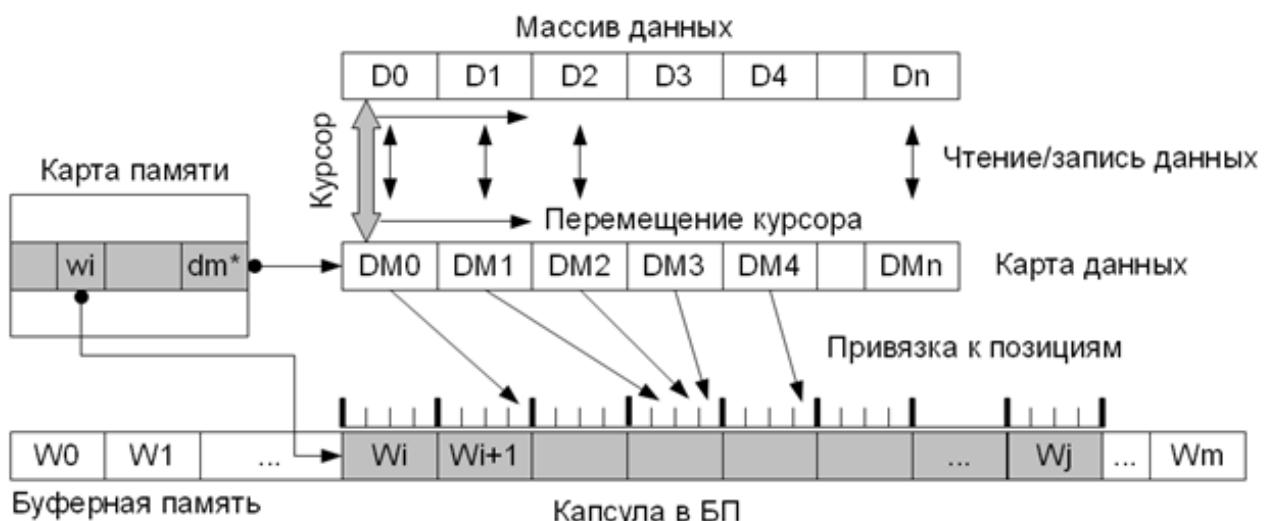

Комбинирование принципов самодостаточности и рекуррентности приводит к тому, что исполняемой программы не существует в МПРА в привычном смысле. Есть только начальное сжатое состояние значений тегов операндов, которые динамически подвергаются рекуррентной развертке. Данное сжатое состояние формирует контекст вычисляемого алгоритма и называется капсулой. Представление решаемой большой задачи в виде совокупности капсул было названо капсульным стилем программирования. Таким образом, МПРА реализует мелкозернистый параллелизм на уровне операндов и крупнозернистый параллелизм на уровне капсул. Очевидно, что разработка программного обеспечения в данном стиле является нетривиальной задачей.

Область ЦОС была выбрана по двум причинам. Во-первых, задачи ЦОС необходимо решать во многих областях человеческой деятельности. Следовательно, разработка вычислительного устройства для задач ЦОС является актуальной. Во-вторых, принципы потоковых архитектур и требования со стороны алгоритмов ЦОС хорошо сочетаются друг с другом в приложениях, для которых характерна высокая степень внутреннего параллелизма.

Основной сдерживающей причиной широкого практического использования такой интеграции является, прежде всего, стоимостной фактор, который делает нецелесообразным прямолинейное использование в них технических решений из области потоковых систем массового параллелизма.

На момент начала выполнения диссертационного исследования МПРА существовала на уровне технической спецификации и небольшого программного прототипа. Результаты предварительной апробации показали, что архитектура имеет высокий потенциал эффективности, но ее существующая структура и набор функциональных возможностей не удовлетворяют требованиям производительности для задач ЦОС реального времени. Поэтому построение высокоэффективной потоковой рекуррентной архитектуры для решения задач ЦОС реального времени, а также разработка элементов методологии программирования и отладки ГАРОС (как самой архитектуры, так и специализированного программного обеспечения), являются необходимыми и актуальными задачами.

**Объект исследования:** рекуррентно-потоковая модель вычислений и архитектура на ее основе.

**Предмет исследования:** структурная организация и алгоритмы функционирования ключевых компонент новой архитектуры, а также методы и средства ее программирования и отладки.

### **Цель и задачи диссертационной работы**

Целью диссертационной работы является разработка элементов потоковой рекуррентной архитектуры и элементов методологии программирования и отладки для создания прототипа устройства рекуррентного обработчика сигналов, который обладает требуемым уровнем производительности для решения задач ЦОС реального времени.

Для достижения поставленной цели необходимо решить следующие задачи:

1) Разработать структурные элементы архитектуры, методы и алгоритмы их функционирования, которые позволяют: эффективно реализовать поддержку параллелизма на различных уровнях; минимизировать избыточность тегированных данных; достичь требуемого уровня производительности для задач ЦОС реального времени.

2) Разработать теоретические основы программируемости ГАРОС, которые включают в себя: методики и алгоритмы реализации различных этапов разработки и отладки ПО; программную и аппаратную поведенческие модели архитектуры для проведения испытаний; набор средств аппаратно-программного моделирования и отладки архитектуры.

3) Осуществить испытания всех разработанных средств путем реализации демонстрационной задачи распознавания изолированных слов и комплекта типовых алгоритмов ЦОС для подтверждения эффективности полученных результатов работы путем сравнения с современным высокопроизводительным сигнальным процессором.

**Научная новизна** диссертационной работы состоит в следующем:

1) Впервые предложены методы и алгоритмы организации суперскалярных вычислений на уровне микроархитектуры вычислительных ядер ГАРОС, учитывающие специфику представления тегированных самодостаточных данных и процесса рекуррентной развертки. Разработанные решения позволяют использовать вычислительные ядра в двух, трех, а в некоторых случаях и в четырех задачном режиме.

2) Впервые предложены методы и алгоритмы реализации аппаратной поддержки алгоритма БПФ, которые учитывают специфику хранения и обработки тегированных самодостаточных данных и суперскалярность вычислительных ядер ГАРОС. Разработанные решения позволяют использовать вычислительные ядра в четырех задачном режиме на протяжении всего процесса вычисления БПФ, а также обеспечивают рациональное использование памяти самодостаточных данных путем максимального снижения их избыточности.

3) Впервые разработаны элементы методологии программирования и отладки ГАРОС, включающие в себя: методики и алгоритмы, комплект моделей и инструментов аппаратно-программного моделирования. Разработанный набор инструментов позволил успешно реализовать задачу распознавания изолированных слов и синтезировать ПЛИС прототип ГАРОС, который позволяет решать эту задачу в реальном времени.

**Методы проведения исследования:** Математическую основу исследования составляют системный анализ, теория алгоритмов, теория графов, теория языков программирования и методы организации архитектур вычислительных систем. Практические результаты диссертации были получены с привлечением таких экспериментальных методов исследования как: имитационное моделирование на программном и аппаратном уровнях; методов разработки и тестирования Test-Driven Development для программных средств и Assertion-Based Design для аппаратных средств; синтез аппаратного прототипа и натурный эксперимент.

**Результаты диссертационной работы** реализованы:

1) в виде комплекта моделей, элементов методологии программирования и отладки ГАРОС, а также комплекта специализированного ПО для проведения испытаний в ходе

выполнения НИР «Информационные, управляющие и телекоммуникационные системы 2017-2021» в рамках государственного задания № 0063-2019-0010 (11) по направлению «Концептуальные и методологические основы создания семейства потоковых самосинхронных процессоров и средств поддержки их проектирования»;

2) в виде ПЛИС прототипа в ходе выполнения гранта РНФ № 19-11-00334 «Инновационная архитектура самосинхронных цифровых сигнальных процессоров, управляемых потоком данных 2019-2021»;

3) в виде программного комплекса моделирования и отладки «ПК ПОТОК» в ходе выполнения научного проекта «Методы построения и моделирования сложных систем на основе интеллектуальных и суперкомпьютерных технологий, направленные на преодоление больших вызовов 2020-2023», финансируемого Минобрнауки по Соглашению № 075-2020-799 от 29 сентября 2020 г.

Результаты диссертационной работы были получены соискателем лично, за исключением аппаратной модели, для которой автор: разрабатывал алгоритмы; проектировал отдельные функциональные блоки; осуществлял тестирование.

### **Личный вклад автора**

Разработанные элементы методологии программирования и отладки ГАРОС в составе методик, алгоритмов, технологий, архитектуры программного комплекса «ПК ПОТОК» и его основных компонент получены соискателем лично. Программная модель прототипа архитектуры, программная реализация «ПК ПОТОК» также разработаны соискателем лично, либо под непосредственным его руководством.

Автор принимал участие в разработке аппаратной модели под руководством Дьяченко Ю.Г. В частности: разрабатывал алгоритмы; проектировал отдельные функциональные блоки; осуществлял тестирование, верификацию и валидацию средствами «ПК ПОТОК».

Под руководством Морозова Н.В. автор также принимал участие в синтезе ПЛИС прототипа, его отладке средствами «ПК ПОТОК» и накоплении и обработке результатов натурных испытаний.

**Теоретическая значимость:** разработаны методы и алгоритмы организации вычислений в рамках МПРА, которые позволили создать эффективный прототип ГАРОС для решения задач ЦОС в реальном времени. Разработаны элементы методологии программирования и отладки ГАРОС, которые позволили организовать полноценный и эффективный процесс программирования и отладки полученного прототипа. Разработанный набор инструментов

может быть использован в качестве основы для дальнейшего развития архитектуры как для применения в области ЦОС, так и для других классов задач.

**Практическая значимость:** создан ПЛИС прототип ГАРОС, который способен эффективно решать задачу распознавания изолированных слов, а также ряда других типовых задач в области ЦОС (различные виды цифровых фильтров, частотный анализ при помощи алгоритма БПФ, алгоритм Витерби кодирования сигнала, поиск минимума/максимума и др.). Полученные результаты могут быть использованы в качестве основы для разработки других вычислительных устройств на отечественной элементной и архитектурной базе.

**Достоверность результатов** обеспечивается:

- корректностью применения выбранных моделей, методов и алгоритмов для разработки, программирования и отладки архитектур вычислительных систем и их прототипов;

- корректностью ограничений и допущений при проведении моделирования;

- достоверностью исходных данных демонстрационной задачи распознавания изолированных слов;

- адекватностью (бит-эквентностью) результатов программного моделирования, аппаратного моделирования и натурного эксперимента над ПЛИС прототипом и исходных данных демонстрационной задачи.

**Апробация результатов работы** выполнена в ряде конференций. Наиболее значимые из них:

- 1) 2016 IEEE Conference of Russian Young Researchers in Electrical and Electronic Engineering (EIConRus), Санкт-Петербург, Россия, 02-03 февраля 2016 г. (индексируется в Scopus).

- 2) Проблемы разработки перспективных микро- и наноэлектронных систем – 2016 (МЭС-2016), Москва, Зеленоград, Россия, 03-07 октября 2016 г. (индексируется в РИНЦ и ВАК).

- 3) IEEE East-West Design & Test Symposium (EWDTs'2016), Ереван, Армения, 14-17 октября 2016 г. (индексируется в Scopus).

- 4) 2017 IEEE Conference of Russian Young Researchers in Electrical and Electronic Engineering (EIConRus), Санкт-Петербург, Россия, 01-03 февраля 2017 г. (индексируется в Scopus).

- 5) 2018 IEEE Conference of Russian Young Researchers in Electrical and Electronic Engineering (EIConRus), Москва, Россия, 29 января – 01 февраля 2018 г. (индексируется в Scopus).

6) Проблемы разработки перспективных микро- и наноэлектронных систем – 2018 (МЭС-2018), Москва, Зеленоград, Россия, 01-05 октября 2018 г. (индексируется в РИНЦ и ВАК).

7) 2019 IEEE Conference of Russian Young Researchers in Electrical and Electronic Engineering (ElConRus), Москва, Россия, 28-31 января 2019 г. (индексируется в Scopus).

8) 2019 IEEE EAST-WEST DESIGN & TEST SYMPOSIUM (EWDTs'2019), Батуми, Грузия, 13-16 сентября 2019 г. (индексируется в Scopus).

9) 2020 IEEE Conference of Russian Young Researchers in Electrical and Electronic Engineering (ElConRus), Москва, Россия, 27-30 января 2020 г. (индексируется в Scopus).

10) 2020 International Conference Engineering Technologies and Computer Science (EnT 2020), Москва, Россия, 24-27 июня 2020 г. (индексируется в Scopus).

11) Проблемы разработки перспективных микро- и наноэлектронных систем — 2020 (МЭС-2020), Москва, Зеленоград, Россия, октябрь 2020 г. (индексируется в РИНЦ и ВАК).

12) 2021 IEEE Conference of Russian Young Researchers in Electrical and Electronic Engineering (ElConRus), Санкт-Петербург, Россия, 26-29 января 2021 г. (индексируется в Scopus).

13) 2021 International Conference Engineering Technologies and Computer Science (EnT 2021), Москва, Россия, 18-19 августа 2021 г. (индексируется в Scopus).

14) IEEE East-West Design & Test Symposium (EWDTs'2021), Батуми, Грузия, 10-13 сентября 2021 г. (индексируется в Scopus).

15) Проблемы разработки перспективных микро- и наноэлектронных систем – 2021 (МЭС-2021), Москва, Зеленоград, Россия, октябрь 2021 г. (индексируется в РИНЦ и ВАК).

16) 2022 IEEE Conference of Russian Young Researchers in Electrical and Electronic Engineering (ElConRus), Санкт-Петербург, Россия, 25-28 января 2022 г. (индексируется в Scopus).

17) Проблемы разработки перспективных микро- и наноэлектронных систем – 2022 (МЭС-2022), Москва, Зеленоград, Россия, октябрь 2022 г. (индексируется в РИНЦ и ВАК).

18) 2023 IEEE Conference of Russian Young Researchers in Electrical and Electronic Engineering (ElConRus), Санкт-Петербург, Россия, 24-27 января 2023 г. (индексируется в Scopus).

Кроме того, соискателем получены 11 свидетельств о регистрации программ и **5** патентов Российской Федерации на изобретение.

**Область исследования** диссертации соответствует требованиям паспорта специальности ВАК Минобрнауки 2.3.2 «Вычислительные системы и их элементы» в части пунктов:

п. 5 – Разработка научных методов и алгоритмов организации арифметической, логической, символьной и специальной обработки данных, хранения и ввода-вывода информации;

п. 7 – Разработка научных методов и алгоритмов организации параллельной и распределенной обработки информации, многопроцессорных, многомашинных и специальных вычислительных систем.

**Публикации.** По теме диссертации автором опубликовано 50 печатных работ, в том числе: 14 публикаций в рецензированных научных изданиях, входящих в системы цитирования Web of Science и Scopus; 24 публикаций в рецензированных научных изданиях, входящих в систему цитирования РИНЦ и перечень ВАК Минобрнауки России («Перечень рецензируемых научных изданий, в которых должны быть опубликованы основные научные результаты диссертаций на соискание ученой степени кандидата наук, на соискание ученой степени доктора наук»); 11 свидетельств о регистрации программ; 3 патента Российской Федерации на изобретение.

**Структура и объем работы.** Диссертационная работа состоит из введения, четырех глав, заключения, списка литературы. Общий объем диссертации – 200 стр., в том числе 156 стр. основного текста, одно приложение, 35 иллюстраций в основном тексте, 16 таблиц в основном тексте. Список литературы состоит из 116 наименований.

#### **Научные положения, выносимые на защиту:**

1) методы и алгоритмы организации вычислительного процесса позволяющие достичь требуемого уровня производительности прототипа архитектуры для задач ЦОС реального времени;

2) структурные элементы архитектуры, а также методы и средства аппаратной поддержки алгоритма БПФ позволяющие минимизировать избыточность тегированных данных, которая является ключевой проблемой потоковых систем, и использовать дорогие элементы памяти рациональным образом;

3) элементы методологии программирования и отладки ГАРОС, позволяющие организовать полноценный и эффективный процесс разработки и отладки ПО для прототипа архитектуры, охватывающие большую часть этапов жизненного цикла ПО и позволяющие существенно сократить непроизводительные затраты разработчиков за счет частичной автоматизации процессов верификации и валидации.

# Глава 1 Исследование потоковой рекуррентной архитектуры и ее прототипа ГАРОС

Современное многообразие и сложность решаемых вычислительных задач потребовала создания большого количества разнообразных моделей вычислений и архитектур вычислительных систем. Часть из них используют схожие базовые механизмы функционирования, в то время как другие – основаны на принципиально других решениях. Однако, большинство этих архитектур объединяет то, что на том или ином уровне они реализуют механизмы эффективной поддержки параллелизма. В главе рассматриваются основные способы организации параллельных вычислений. Рассматриваются ключевые принципы потоковой модели вычислений. Приводится анализ характерных проблем реализации потоковых архитектур и существующих подходов их решения. Представлена классификация существующих вычислительных систем или их прототипов на основе потоковой архитектуры.

Рассматриваются концептуальные основы рекуррентно-потоковой модели вычислений и ключевые особенности ее прототипа ГАРОС. Обозначается место архитектуры в классификации потоковых архитектур. Также в главе приводится сравнительный анализ ГАРОС и других отечественных архитектур, основанных на потоковой модели вычислений. Ставятся задачи диссертационного исследования.

## 1.1 Параллельные вычислительные системы

Любая вычислительная система реализует некоторый вычислительный процесс. Все процессы, выполняемые в вычислительных системах, могут быть распределены по двум основным категориям: последовательные и параллельные.

Последовательный вычислительный процесс характеризуется тем, что в каждый момент времени вычислительная система может исполнять только один из дочерних процессов. Такие вычислительные системы еще называются однозадачными или скалярными.

Параллельный вычислительный процесс характеризуется тем, что в каждый момент времени вычислительная система может исполнять один или более дочерних процесса одновременно. Такие вычислительные системы называются многозадачными (суперскалярными). Дочерние процессы, которые одновременно имеют активное состояние, называются параллельными процессами соответственно.

По мере развития теорий вычислений и проектирования вычислительных систем стало очевидно, что производительности машин, основанных на использовании последовательного вычислительного процесса, недостаточно для покрытия возрастающей сложности задач, решаемых с их помощью. В связи с этим, со второй половины XX века в мире ведутся работы и

исследования, направленные на разработку архитектур, реализующих параллельный вычислительный процесс.

Идея параллельных вычислений возникла и обсуждается в научном сообществе уже давно. В 1958 году Гилл (Gill) написал работу [1], посвященную проблемам параллельной обработки информации, которую можно считать одной из наиболее ранних в этой области. Следует отметить, что эксплуатация параллелизма – очевидное на первый взгляд решение по увеличению производительности, сопряжено с большим количеством проблем [2].

### 1.1.1 Классификация параллельных архитектур Кришнамарфи

Разнообразие моделей вычислений и основанных на них архитектур вычислительных систем привело к необходимости создания соответствующих классификаций. В книгах Воеводина В.В. и Михайлова Б.М. приводится подробное описание большинства классификаций [2, 3]. Наиболее полной с точки зрения классификации параллельных вычислительных систем является классификация Е. Кришнамарфи. Кришнамарфи предложил использовать четыре основные характеристики:

1. степень гранулярности;

2. способ реализации параллелизма;

3. топология и природа связи процессоров;

4. способ управления процессорами.

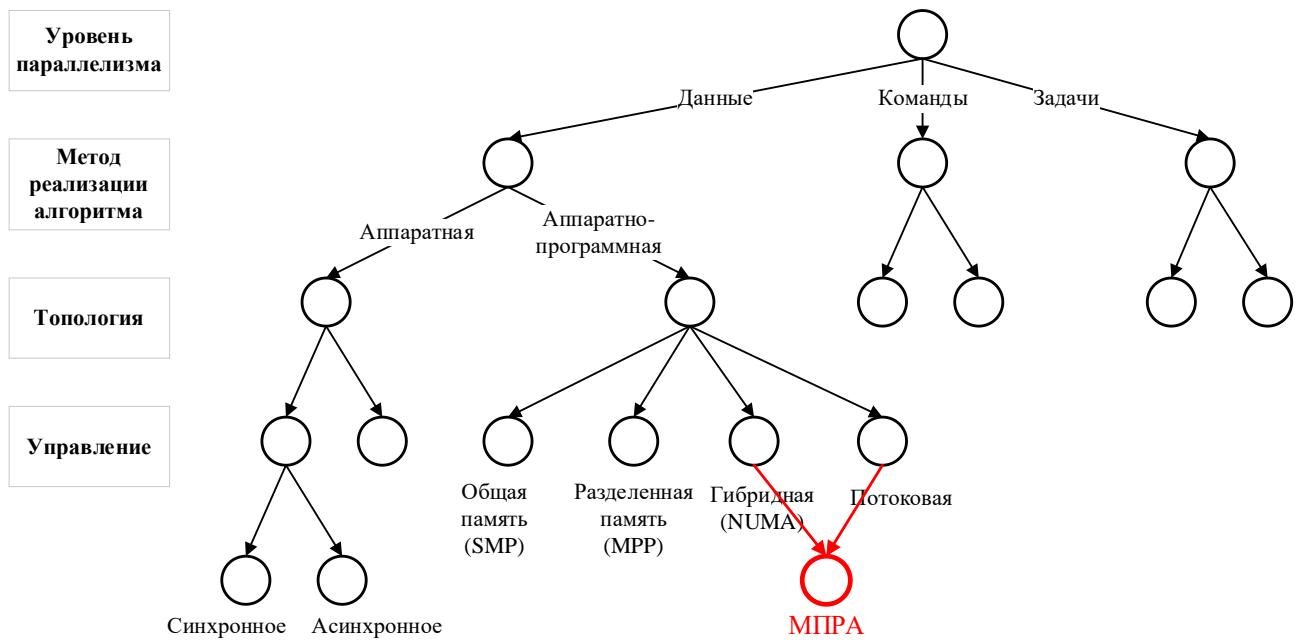

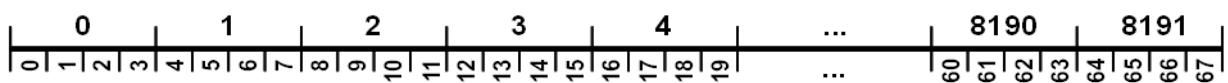

Построения классификации осуществляется в соответствии со следующим алгоритмом. Для каждой степени гранулярности рассматриваются все возможные способы реализации параллелизма. Для каждого полученного варианта рассматриваются все комбинации топологии связи и способов управления процессорами. В результате получается дерево, представленное на рисунке 1.1, в котором каждый ярус соответствует своей характеристике, каждый лист представляет отдельную группу компьютеров в данной классификации, а путь от вершины дерева однозначно определяет значения указанных выше характеристик. На рисунке также отмечено, к каким классам параллельных архитектур относится МПРА.

Несмотря на то, что классификация Е. Кришнамарфи построена лишь на четырех признаках, она позволяет выделить и описать такие "нетрадиционные" параллельные системы, как систолические массивы, потоковые машины и др. Но эта простота является и основной причиной ее недостатков. Некоторые архитектуры нельзя однозначно отнести к тому или иному классу, например, компьютеры с архитектурой гиперкуба и ассоциативные процессоры. Для более точного описания таких машин потребуется ввести еще целый ряд характеристик, таких, как размещение задач по процессорам, способ маршрутизации сообщений, возможность реконфигурации, аппаратная поддержка языков программирования и другие.

Рисунок 1.1 – Классификация Кришнамарфи

### 1.1.2 Способы организации параллельных вычислений

#### 1.1.2.1 Параллельная обработка данных

Архитектуры, построенные согласно данному принципу, описывают процесс вычислений в виде взаимодействия совокупности конечного множества идентичных вычислительных устройств, каждое из которых решает некоторую часть поставленной задачи. При этом общая производительность системы при такой организации вычислений ограничивается сверху в соответствии с законом Амдала [4]. По способу организации коммутационной среды выделяют следующие типы моделей параллельных вычислений [5]:

1) **Процесс/канал.** В этой модели программы состоят из одного или более процессов, распределенных по процессорам. Процессы выполняются одновременно, их число может изменяться в течение времени выполнения программы. Процессы обмениваются данными через каналы, которые представляют собой односторонние коммуникационные линии, соединяющие только два процесса. Каналы можно создавать и удалять.

2) **Общей памяти.** В этой модели все процессы совместно используют общее адресное пространство. Процессы асинхронно обращаются к общей памяти с запросами чтения/записи, что создает проблемы блокировки памяти. Для управления доступом к общей памяти используются стандартные механизмы синхронизации - семафоры и блокировки процессов. Архитектуру параллельных вычислительных систем с общей памятью называют также симметричной многопроцессорной архитектурой (symmetric multiprocessing – SMP).

3) **Разделенной памяти.** В этой модели каждый процессор имеет собственную оперативную память, которая хранит исполняемую программу и связанные с ней данные.

Взаимодействие между процессорами осуществляется путем обмена, используя подпрограммы приема/передачи данных некоторой коммуникационной системы. Архитектуру параллельных вычислительных систем с разделяемой памятью также называют массивно-параллельной (massive parallel processing – MPP).

4) Неоднородной памяти (non uniform memory access - NUMA). Данная модель является гибридной и объединяет в себе принципы общей и разделенной памяти. Память физически распределена по различным частям системы, но логически она является общей. Система построена из однородных базовых модулей, состоящих из небольшого числа процессоров и блока памяти. Модули объединены с помощью высокоскоростного коммутатора. Поддерживается: единое адресное пространство; аппаратный доступ к удаленной памяти, т.е. к памяти других модулей. Доступ к локальной памяти осуществляется в несколько раз быстрее, чем к удаленной. Другими словами, NUMA является MPP архитектурой, где в качестве отдельных вычислительных элементов берутся SMP-узлы.

5) Параллелизм данных (векторная обработка). В этой модели единственная программа задает распределение данных между всеми процессорами компьютера и операции над ними. Распределенными данными обычно являются массивы (вектора). Как правило, языки программирования, поддерживающие данную модель, допускают операции над массивами, позволяют использовать в выражениях целые массивы и фрагменты массивов. Распараллеливание операций над массивами позволяет увеличить производительность программы. Компилятор отвечает за генерацию кода, осуществляющего распределение элементов массивов и вычислений между процессорами. Каждый процессор отвечает за то подмножество элементов массива, которое расположено в его локальной памяти.

#### 1.1.2.2 Параллелизм на уровне инструкций

Основными методами реализации параллелизма уровня инструкций являются [6]:

##### 1) Конвейерная обработка инструкций

Данный метод является наиболее распространенным и используется в подавляющем большинстве микроархитектур процессоров. Благодаря разбиению процесса выполнения инструкции на короткие по длительности стадии достигается высокий уровень тактовой частоты. В тоже время, реализация техники одновременного исполнения разных стадий разных инструкций в один и тот же такт позволяет значительно повысить пропускную способность процессора и его производительность в целом. Однако у данного подхода есть и свои проблемы.

Первая проблема заключается в возникновении конфликтов доступа к одним и тем же ресурсам процессора различными инструкциями, которые находятся на разных стадиях исполнения. Возникает она, когда имеет место зависимость по данным между инструкциями. Данная проблема может решаться с помощью пересылки (bypass – байпаса) промежуточного

результата зависимой инструкции до его записи в регистровый файл. Если же байпас невозможен, то необходимо приостанавливать конвейер. Приостановка конвейера, очевидно, приводит к задержкам и потери производительности.

Вторая проблема заключается в возникновении конфликтов управления – т.е. при необходимости выполнить условный переход. Данное событие является очень разрушительным для конвейерной обработки. Для его обработки не только производится приостановка, но и также сброс состояния конвейера, инициализация нового архитектурного состояния и заполнение конвейера. Зачастую, обработка перехода приводит к потерям сотен тактов на перенастройку.

## 2) Предсказание переходов

Данный метод используется для раннего вычисления условий переходов с помощью специальных аппаратных средств, которые пытаются «предсказать» на основе накопленной истории какую следующую инструкцию необходимо обработать. Если предсказание оказалось верным, то конвейер продолжает функционирование в текущем состоянии. В противном случае, осуществляется очистка конвейера от неверных инструкций. С целью минимизировать количество инструкций, которые необходимо очистить, логика вычисления условий переходов перемещается в начало конвейера.

## 3) Спекулятивные вычисления

Спекулятивные вычисления – это набор методов, направленных на улучшение механизма предсказания переходов, рассмотренного ранее. Суть их заключается в вычислении заранее всей ветки, либо её части, еще до того, как будет известно, выполнится она или нет. Данный подход позволяет существенно снизить задержки переключения контекстов при переходе. Несмотря на свою эффективность, опережающие вычисления создают уязвимость с точки зрения безопасности, т.к. в архитектурном состоянии одновременно присутствуют обе ветки вычислений. С этой уязвимостью столкнулись все крупные разработчики процессоров, позволяя злоумышленникам получить доступ к фрагментам регистров памяти с привилегированным доступом из процесса общего доступа [7].

## 4) Суперскалярная микроархитектура

Еще один широко распространенный метод повышения характеристики *instruction per cycle* (IPC) – количества выполняемых инструкций в такт. Он заключается в том, что в состав микроархитектуры процессора вводится несколько блоков АЛУ, несколько блоков сдвига и округления и т.п. Данные блоки располагаются таким образом, что могут работать параллельно. Следовательно, процессор может за один такт выполнять сразу несколько инструкций на всех блоках (называемых также каналами). Данную характеристику еще называют *multi-issue* (многозадачность).

Совмещение методов конвейерного исполнения команд (временного параллелизма) и суперскалярности (пространственного параллелизма) позволяет добиться впечатляющего уровня производительности. Однако существующие проблемы конвейерной обработки лишь усугубляются при использовании данного подхода. В частности, помимо конфликтов «запись после чтения» (характерных для всех конвейерных процессоров) при использовании метода внеочередного выполнения инструкций возникают также конфликты «чтение после записи» и «запись после записи». Данные конфликты в большинстве случаев привносятся программистом и возникают в случае зависимости по данным между инструкциями.

Разрешение конфликтов в суперскалярной микроархитектуре требует использования либо мощного компилятора, который может эффективно упорядочивать инструкции для обеспечения максимальной пропускной способности конвейера и характеристики IPC, либо существенных трудозатрат программиста для ручной оптимизации кода.

В реальных программах встречается много зависимостей по данным, поэтому суперскалярные процессоры с высоким параметром multi-issue редко могут использовать все свои функциональные блоки полностью. Более того, большое количество функциональных блоков и сложности с организацией байпаса требуют множества дополнительных логических элементов и потребляют значительное количество электроэнергии [6].

#### 5) Внеочередное выполнение инструкций

Данный метод является дополнением к суперскалярной микроархитектуре и используется для повышения характеристики IPC. Достигается это путем введения в процессор специализированной логики, которая осуществляет опережающий просмотр большого количества инструкций для скорейшего обнаружения и запуска тех из них, которые являются не зависимыми по данным. Порядок запуска инструкций при этом не сохраняется, но процессор учитывает все зависимости, что позволяет правильно вычислить результат.

#### 6) Переименование регистров

Ранее было отмечено, что при внеочередном выполнении инструкций суперскалярным процессором могут возникать конфликты «запись после чтения» и «запись после записи». Оба этих конфликта не являются неустранимыми и возникают как результат работы программиста или компилятора. Для устранения данных конфликтов используется метод переименования регистров. Суть его заключается в том, что в состав процессора помимо регистров архитектурного состояния вводятся также неархитектурные регистры, которые напрямую не доступны программисту. При обнаружении процессором одного из этих конфликтов происходит переименование (подмена ссылки) указанного в инструкции регистра на один из свободных неархитектурных регистров.

#### 7) Very Long Instruction Word (VLIW)

Данный метод является разновидностью суперскалярной реализации, который основан на концепции «вычисления с явным параллелизмом машинных команд» (explicitly parallel instruction computing – EPIC) [8]. Загрузка вычислительных ресурсов возлагается управляемся компилятором, что позволяет снизить аппаратные расходы. Получаемая таким образом программа реализует статическое распределение ресурсов. Данный подход также имеет свои недостатки. Во-первых, отсутствует обратная совместимость программ в случае обновления архитектуры. Во-вторых, построение эффективного VLIW-компилятора – это NP-полнная задача, для решения которой на сегодняшний день существуют только эвристические методы.

#### 8) SIMD инструкции

Данный способ обработки позволяет одной инструкции обрабатывать сразу серию данных. Этот метод эффективен, когда входные данные имеют небольшую размерность и могут быть упакованы в длинное 32 или 64 разрядное слово. Сама инструкция выполняется на одном из вычислительных блоков над этим словом (словами), интерпретируя их как несколько пар входных данных. Для этого требуется небольшая модификация вычислительных блоков. Например, такую технику используется в цифровых сигнальных процессорах (ЦСП) Texas Instruments для выполнения двух операций сложения 32-битных чисел на 64-битном АЛУ.

##### 1.1.2.3 Параллелизм на уровне потоков

Основные методы реализации параллелизма уровня потоков [9]:

###### 1) Временная многопоточность

При таком методе реализации многопоточности процессор хранит состояния сразу нескольких потоков. Однако в каждый такт может выполнять только один из них. Существует два основных подвида временной многопоточности: крупнозернистая и тонкозернистая.

Крупнозернистая многопоточность характеризуется тем, что в конвейере процессора исполняется только один поток в течение достаточно продолжительного промежутка времени. Когда этому потоку необходимы данные или спустя заданное количество тактов, процессор сохраняет состояние потока и переключается на другой поток, данные для которого уже готовы.

При тонкозернистой реализации многопоточности процессор переключается между потоками каждый такт. Таким образом, гарантируется исполнение всех потоков ценой замедления исполнения каждого отдельного. Общая пропускная способность увеличивается. Данная реализация требует, чтобы потоки были слабо взаимосвязаны или не связаны вовсе.

###### 2) Одновременная многопоточность

Данный метод организации многопоточности реализуется на конвейерных суперскалярных процессорах. Он позволяет решить проблему низкой IPC суперскалярных процессоров путем исполнения одновременно нескольких различных потоков, тем самым минимизируя эффект зависимостей инструкций по данным. Преимуществом данной реализации

многопоточности является существенно более высокая производительность, в то время как временная многопоточность имеет более низкое энергопотребление и, следовательно, тепловыделение. Известным примером реализации одновременной многопоточности является технология Hyper-threading, используемая в процессорах компании Intel.

#### 1.1.2.4 Потоковая модель вычислений

Появление потоковых архитектур связано с развитием архитектур параллельных вычислительных систем. Поэтому, класс потоковых архитектур является подмножеством класса архитектур параллельных вычислительных систем. Модель потока данных [10-13] была предложена как альтернатива последовательной модели вычислений фон Неймана.

Фундаментальные принципы потока данных были разработаны Джеком Денисом (Jack Dennis) в начале 1970-х годов. Модель потока данных отменяет два свойства модели фон Неймана – счетчик команд и глобальную обновляемую память, - которые стали узким местом в использовании параллелизма [14]. Правило вычислений, известное также как «правило срабатывания» модели потока данных, определяет условие исполнения команды. Основное правило срабатывания, общее для всех систем потока данных, заключается в следующем: команда считается готовой к исполнению, когда ей доступны все входные операнды, необходимые для ее исполнения. Говорят, что команда запущена на исполнение, если для нее выполняется это условие. Результатом запуска команды является потребление значений входных операндов и генерация значений выходных операндов.

## 1.2 Анализ потоковой модели вычислений и проблем ее реализации

### 1.2.1 Принципы потоковой модели вычислений

Большинство ранних проектов в мире по разработке прототипов потоковых архитектур были основаны на работе Dennis [15]. В рамках данной работы автор заложил фундаментальные принципы нового языка программирования, который предназначен для описания вычислительных процедур, основанных на концепции управления потоком данных. Согласно этой концепции, вычислительный процесс организован таким образом, что выборка и исполнение очередной инструкции осуществляется при условии готовности требуемых для нее данных. Данный подход позволяет отказаться от использования счетчика команд и глобальной обновляемой памяти. Каждая инструкция устанавливает однозначное соответствие каждому конкретному набору входных данных – набор выходных данных.

Потоковая модель вычислений – это абстрактная модель вычислений, которая реализует вычислительный процесс, запрограммированный с помощью языка потокового программирования. Данной модели характерны следующие фундаментальные принципы:

- 1) Вычислительный процесс представляется в виде направленного графа, в котором вершины обозначают инструкции, а дуги – перемещаемые между инструкциями данные;

- 2) Данные снабжаются специальными контейнерами – *токенами*, которые перемещаются по дугам графа;

- 3) Условием исполнения узла графа, называемым также «правилом срабатывания», является наличие токенов на **всех** входных дугах;

- 4) Результат выполнения узла графа – это чистая функция входных значений, т.к. гарантируется отсутствие неявных взаимодействий между узлами посредством побочных эффектов (например, через разделяемую память);

- 5) Следствием п.п. 4) является свойство потоковой программы, которое заключается в преобразовании каждого единственного набора входных данных в ровно один набор выходных данных. Этот принцип также называется *правилом однократного присваивания*. Потоковый граф, который обладает данным свойством называется *хорошо-структурированным* (*well-behaved*);

- 6) Локализованность вычислений –инструкции в потоковом графе не имеют «длинных» зависимостей по данным. Другими словами, каждый токен является локальным и существует в рамках своего фрагмента потокового графа. Связь с другими фрагментами графа осуществляется только посредством входных и выходных дуг.

Рассмотренные принципы формируют два ключевых свойства потоковой модели вычислений: естественная поддержка параллелизма и детерминизм. Под естественной поддержкой параллелизма понимается возможность одновременного исполнения всех независящих между собой по данным узлов потокового графа (мелкозернистый параллелизм). Детерминизм потоковой модели заключается в том, что, независимо от порядка исполнения узлов графа, гарантируется получение корректного результата вычислений.

В современных фон-неймановских архитектурах потоковые принципы нашли отклик в виде принципа внеочередного исполнения команд, где окно исполнения линейно и последовательно продвигается в соответствии с принципами архитектуры, однако в рамках данного окна, инструкции могут быть исполнены в порядке готовности данных.

### **1.2.2 Структурные элементы потоковой модели вычислений**

Аналогично другим абстрактным моделям вычислений – потоковая модель включает в себя набор инструментов, обеспечивающих ей эквивалентную вычислительную мощность. К данным инструментам относятся: множество допустимых инструкций (система команд); множество допустимых атомарных типов данных; способы построения сложных структур данных; средства поддержки условных переходов и циклических вычислений; средства поддержки определяемых программистом функций; способы организации памяти. В отличие от

классической модели вычислений и архитектуры, предложенных фон-Нейманом, реализация данных инструментов в потоковой модели имеет свои специфические особенности.

### *Система команд и организация ветвления*

Основой потоковой модели вычислений, как уже было отмечено ранее, является направленный потоковый граф, удовлетворяющий критерию *хорошей структурированности*. Как показано в работах [11, 15] данному критерию удовлетворяют все ациклические потоковые графы для арифметических и логических операций. Поэтому, система команд потоковой модели включает в себя минимально необходимый набор арифметических и логических операций аналогичный другим абстрактным моделям. Операции условного перехода и организация циклических процедур нарушают условия критерия структурированности потокового графа. Для преодоления данного ограничения в состав системы команд необходимо было ввести специализированные операторы, названные авторами классических работ – *switch* и *merge*.

Оператор *switch* принимает на вход анализируемое значение и управляющий сигнал, который имеет логическое значение. В зависимости от значения управляющего сигнала *True* или *False*, оператор *switch* порождает ровно один токен, который он отправляет на один из выходов – *True* или *False* соответственно. Оператор *merge*, получает на входы логические значения *True* или *False* от каждой из веток вычислений и осуществляет выбор одного из них по значению входного управляющего сигнала, объединяя тем самым ветки вычислений.

Сами по себе данные операторы не являются *well-behaved*, однако, их применение позволяет строить потоковый графы, удовлетворяющий данному критерию. Существует еще одна особенность применения данных операторов при построении циклических программ. Если тела циклов достаточно большие или не зависят друг от друга по данным, то, в силу естественной поддержки параллелизма в потоковой модели, в процессе вычислений может быть создано большое количество графов тел цикла, каждое из которых будет иметь свой контекст номера итерации. Данное поведение также называют *динамическим разворачиванием циклов*.

### *Типы и структуры данных*

Исходное описание потоковой модели вычислений включает в себя следующие атомарные типы данных: логический (*boolean*), целые числа (*integer*), действительные числа (*real*) и строки (*strings*). Построенная таким образом потоковая модель вычислений обладает свойством Тьюринг-эквивалентности, как показано в работе [16]. Однако, ее применение было бы в существенной степени ограниченным, в силу отсутствия поддержки структур данных.

В качестве решения данной проблемы авторами в [15] было предложено рекурсивное построение сложных структур данных на основе атомарных. Для этого структура данных должна быть представлена в виде конечного множества пар вида:

$$[\langle s_1: v_1 \rangle, \dots, \langle s_k: v_k \rangle] \quad (1.1)$$

где  $s_i$  – это селекторы, которые могут иметь тип «целые» или «строка», а  $v_i$  – это данные, которые могут быть либо атомарного типа, либо структурой данных. Пустое множество также является структурой данных и обозначается специальным символом `nil`. Полученная структура данных несет в себе некоторую избыточность. Поэтому в работе [11] она была упрощена до множества из двух пар с селекторами *first* и *rest* соответственно.

Построение этой структуры данных осуществляется с помощью специальных операторов в системе команд: *cons* – объединяет пару данных и снабжает их селекторами *first* и *rest*; *append* – является расширением *cons* для построения массивов. Очевидно, что при рекурсивном построении полученные структуры данных могут быть очень большими, поэтому потоковая модель должна предусматривать возможность передачи по дугам токенов большого объема. На практике, как правило, токены несут в себе ссылки на реальные данные, что позволяет значительно уменьшить требования по памяти. Для доступа к элементам структуры данных в систему команд вводится оператор *select*, который осуществляет выборку данного с требуемым значением селектора.

### Функции и процедуры

Возможность определения и вызова функций, определенных программистом, является необходимым элементом любого современного языка программирования. На уровне потокового графа функция – это инкапсуляция фрагмента этого графа в некоторую абстракцию. К данной абстракции применяются те же требования, что и для потокового графа. Во-первых, инкапсулированный фрагмент графа должен удовлетворять критерию *well-behaved*. Во-вторых – исходный потоковый граф после подстановки функции должен также удовлетворять критерию *well-behaved*.

Таким образом, нерекурсивные функции могут быть поддержаны на этапе компиляции. Для более обобщенной поддержки функций в потоковой модели необходимо ввести в систему команд оператор *apply*. Данный оператор получает на вход абстракцию функции, которая описывает некоторый потоковый граф, и набор входных токенов, после чего осуществляет вызов этой функции на заданном наборе токенов.

Реализация оператора *apply* сопряжена с рядом проблем. Например, в какой момент времени необходимо создавать потоковый граф, который соответствует вызываемой функции (когда пришли все входные токены или только один конкретный)? Кроме того, независимо от выбранной реализации, архитектура должна поддерживать динамическое расширение исполняемого потокового графа и методы маршрутизации токенов на дуги вновь созданного

графа. Также может возникнуть потребность повторного использования копии созданного графа, следовательно, необходимо поддерживать разделение контекстов для различных вызовов.

#### *Основной цикл вычислений*

Организация основного цикла исполнения инструкций в потоковой модели вычислений является прямым следствием принципов ее функционирования. Таким образом, можно выделить следующие этапы цикла:

1. Определение готовности узла графа к исполнению (по готовности токенов).

2. Определение инструкции, которую необходимо выполнить.

3. Вычисление результата.

4. Формирование токена результата.

По утверждению авторов в [11] данный цикл является базовым для любой потоковой машины. Однако, его реализация в конкретной архитектуре несет в себе большую гибкость.

В отличие от классической модели фон-Неймана, исполнение инструкций в потоковой модели зависит от прибытия операндов и соответствующих им токенов. Следовательно, задачи управления хранилищем токенов и планирования выполнения инструкций тесно связаны в любой потоковой архитектуре. Другим важным наблюдением является тот факт, что потоковые графы эксплуатируют два вида параллелизма в процессе исполнения инструкций: пространственный параллелизм (любые два узла могут быть выполнены одновременно при условии отсутствия зависимости по данным); временной параллелизм (заключается в конвейеризации независимых вычислительных потоков через один и тот же граф).

### **1.2.3 Характерные проблемы реализации потоковых архитектур**

#### *Проблема организации памяти токенов*

В предыдущем разделе уже были рассмотрены некоторые проблемы реализации потоковой модели вычислений в конкретной архитектуре. Однако, наиболее существенной является проблема разработки механизма хранения и обработки токенов. Потоковая модель вычислений подразумевает, что дуги графа представляют собой FIFO неограниченного размера, что, очевидно, невозможно на практике. Поэтому были разработаны и исследованы два основных подхода к решению проблемы организации памяти токенов.

Первый подход называется *статический поток данных*. Основное ограничение в статической потоковой архитектуре заключается в том, что не более одного токена может быть размещено на дуге потокового графа в каждый момент времени. Для удовлетворения данного ограничения необходимо также модифицировать «правило срабатывания» таким образом, чтобы активация узла графа была возможна только в том случае, когда все выходные дуги узла свободны. Введение данных ограничений позволяет значительно снизить накладные расходы для памяти токенов и выделять ее в объеме, необходимом непосредственно для выполнения

конкретного потокового графа. Однако, для обеспечения корректной работы вычислительной машины на основе статической потоковой архитектуры токены на дугах должны быть физически упорядочены. Кроме того, столь жесткое ограничение приводит к низкой реентерабельности потокового графа и снижению производительности системы в целом [17].

Второй подход был назван *динамический поток данных* или *тегированные токены*. Суть данного подхода заключается в предоставлении возможности активации одного и того же узла потокового графа одновременно. Данный эффект достигается за счет динамического прикрепления к токенам дополнительной информации, называемой тегом. Тегированные токены несут в себе информацию: выполняемом в данный момент потоковом графе, адресе выполняемой инструкции, контексте выполняемой функции, контексте текущей итерации цикла. «Правило срабатывания» активируется при условии совпадения тегов у двух токенов.

Такая организация вычислительного процесса позволяет поддерживать только логический порядок хранения токенов на дугах потокового графа, независимо от физического времени их появления. Основная проблема реализации данного подхода заключается в необходимости создания очень большого по объему и скорости работы ассоциативного хранилища памяти, которое обеспечивает поиск совпадающих пар тегов [17]. Авторы в работе [11] дают оценку физического объема хранилища порядка 100 тысяч токенов, а также необходимого для работы с ним виртуального пространства, адресуемого 40 или более битным адресом.

#### *Проблема построения структур данных*

В потоковой модели существует определенная проблема при работе со структурами данных. Так как в модели отсутствует глобальная разделяемая память, то все токены (согласно принципам функционального программирования) обладают свойством неизменяемости. С одной стороны, это позволяет избегать типовых проблем гонок и тупиков в параллельной вычислительной системе. С другой – приводит к необходимости создания новых токенов и соответствующих им структур данных при попытке изменения уже существующих токенов.

Таким образом, вычислительная система, построенная на основе потоковой модели, должна иметь значительный объем активной памяти токенов для обеспечения корректного функционирования. Кроме того, постоянная генерация новых токенов и структур данных сопряжены с существенными временными затратами и общим снижением производительности вычислительных систем потоковой архитектуры.

#### *Проблема распределения вычислительной нагрузки*

Аналогично традиционным архитектурам вычислительных систем в потоковых архитектурах существует проблема распределения фрагментов исполняемой программы между их вычислительными блоками. Очевидно, что оптимальное распределение задач между вычислительными блоками оказывает прямое влияние на общий уровень производительности

потоковой архитектуры в целом. Однако данная проблема не имеет тривиального решения, т.к. в работе [18] показано, что это NP-полная задача. Основными задачами, которые необходимо решать при распределении нагрузки являются: *разбиение* (графа на подграфы) и *назначение* (каждого подграфа для исполнения на конкретном вычислительном модуле).

#### *Проблема конвейеризации последовательных вычислений*

В работе [11] авторы отмечают, что важной характеристикой вычислительной системы на основе потоковой архитектуры является использование параллелизма для сокрытия задержки коммуникации между вычислительными блоками. Подобное также верно и для сокрытия задержек конвейера для выполнения инструкций, которые имеют зависимость по данным между собой. Однако данное утверждение корректно только при условии, что на каждом вычислительном блоке загружено достаточное количество активных для исполнения пакетов инструкций (для которых активировалось «правило срабатывания»).

Потоковая модель вычислений подразумевает эффективную реализацию мелкозернистого параллелизма и является функциональной. Это означает, что в рамках абстрактной модели вычислительные блоки не должны иметь состояния (т.е. регистров или памяти). Тогда в результате вычислений всегда будут формироваться токены, которые будут отправляться в коммутационную среду и, тем самым, проходить все стадии конвейера для участия в последующих вычислениях.

В случае, если выполняемая задача обладает низкой степенью параллелизма или вообще является последовательной, то даже на одном вычислительном блоке готовые для исполнения пакеты инструкций будут отсутствовать. Следовательно, время выполнения очередной инструкции будет определяться глубиной конвейера, что приведет к крайне низкой производительности при решении последовательных задач.

#### *Проблема поддержки высокопроизводительной микроархитектуры*

Для достижения наилучшей производительности современные процессоры реализуют сложную микроархитектуру. Высокопроизводительная микроархитектура обладает высокой пропускной способностью инструкций, низким временем простоя вычислительных блоков и высокой степенью наполнения конвейера. Достигается это за счет реализации рассмотренных в разделе 1.1.2 механизмов. Концепция внеочередного исполнения команд является частью потоковой модели вычислений и поэтому поддерживается интуитивным образом. Более того, именно исследования в области потоковых архитектур привели к ее внедрению в процессоры традиционной архитектуры. Однако реализация в потоковых архитектурах других способов извлечения параллелизма уровня инструкций сопряжена со множеством проблем.

Условные переходы в потоковой модели вычислений обрабатываются совершенно иначе в сравнении с традиционными архитектурами. Потоковый граф требует вычисления обеих

ветвей с последующим выбором полученного результата. Поэтому невозможно предсказать переход и заранее подготовить пакеты инструкций, которые могли бы быть выполнены из-за того, что их активация возможна только после формирования токена результата перехода.

Суперскалярные вычисления подразумевают выполнение на одном вычислительном блоке более одной инструкции на каждом шаге, которые могут использовать в качестве источников данных внутренние регистры. Также для выполнения некоторых стандартных инструкций требуется сохранять результат накопления в каком-либо регистре состояния. Как было отмечено ранее, вычислительные блоки «классической» потоковой архитектуры не должны иметь состояния, что противоречит предыдущему наблюдению. Кроме того, узлы потокового графа могут нести в себе только одну инструкцию.

Тэгированные данные несут в себе достаточно большой объем избыточной информации, необходимой для однозначной идентификации токена. Поэтому, инструкции потокового графа, которые содержат описание ожидаемых для обработки токенов также имеют большой объем. Увеличение размера пакета инструкций для организации суперскалярных вычислений может стать непреодолимым препятствием для физической реализации таких инструкций.

#### *Проблема обработки константных данных*

Согласно принципу *однократного присваивания* потоковой модели вычислений токены на входе узла потокового графа поглощаются (т.е. удаляются), а результат выполнения инструкции формирует новые токены. Таким образом, токены, которые несут в себе константные данные, должны каким-то образом сохраняться и циркулировать в потоковой архитектуре. В работе [11] приводится описание решения, в котором константные данные кэшируются в программной памяти и извлекаются из нее при выполнении инструкции. При такой организации константные данные уже перестают быть токенами и участвовать в активации *firing-rule*. Кроме того, данное решение усложняет кодировку инструкций.

#### **1.2.4 Реализация структур данных в потоковых архитектурах**

С целью обеспечения функциональности создания, хранения и обработки сложных структур данных (таких как массивы) при условии сохранения основных принципов потоковой модели вычислений был разработан ряд подходов решения рассматриваемой проблемы. К двум основным подходам представления массивов и аналогичных им структур данных относятся: *прямой* и *непрямой* доступ [19]. В схеме *прямого доступа* элементы массива интерпретируются как отдельные токены, что позволяет убрать необходимость реализации массива, как специальной структуры данных. В свою очередь, в схеме *непрямого доступа* массивы хранятся в специальной памяти, а доступ к ним осуществляется явным образом с помощью специальных операторов «чтение» и «запись».

#### 1.2.4.1 Схема прямого доступа – переименование токенов

Организация схемы *прямого доступа* к элементам структуры данных типа массива осуществляется с помощью механизма *переименования токенов*. Суть данного механизма заключается в переименовании тегов, ассоциированных с каждым токеном в массиве, за счет чего достигается прямая пересылка данных массива его потребителю. Это позволяет преобразовать массив в множество индивидуальных токенов. Реализация такой схемы требует ввода в вычислительный процесс специальной функции переименования, которая обычно не известна заранее и трудно получаема в процессе компиляции [19]. Поэтому ее вычисление симулируется с помощью специальной техники.

Схема прямого доступа совместима с основными принципами потоковой модели вычислений. Следовательно, ее использование приводит к построению более однородной архитектуры и дает более высокую производительность, в силу того что нет нужды обрабатывать токены с данными с помощью специального контроллера структур данных. Тем не менее, для данной схемы характерны два узких места. Во-первых, поддержка концепции выполнения инструкций, которые не имеют побочных эффектов, приводит к тому, что структура данных целиком должна быть передана от одного узла графа к другому или даже размножена для множества узлов. Это приводит к значительному росту требований к объему хранилища токенов в блоке их сопоставления. Во-вторых, далеко не всегда можно трактовать нотацию массива как единой сущности, которую можно преобразовать в множество отдельных токенов.

Далее будут рассматриваться схемы *непрямого доступа*.

#### 1.2.4.2 Куча

В статической потоковой машине, разработанной в МИТ, массивы были представлены в виде направленного ациклического графа, который хранится в отдельной вспомогательной памяти [20]. Такой ациклический граф (также называемый *кучей*) всегда образует древовидную структуру с одним корневым элементом, которая обладает свойством, что каждый лист графа достижим из корня. Массивы в рамках данной схемы интерпретируются как указатель на вершину дерева. Это позволяет значительно сократить объем пересылаемых между узлами токенов (вместо всей структуры данных целиком только указатель на нее). Основная идея использования кучи заключается в исключении излишнего копирования путем разрешения совместного использования одних и тех же вложенных структур несколькими структурами данных, что является несомненным преимуществом использования *кучи*.

Тем не менее, представление массивов в виде деревьев не лишено недостатков. Наиболее очевидным недостатком является долгое время доступа к элементам дерева. Как известно, линейно организованные массивы имеют константное время доступа. Древовидная же структура имеет  $O(\log(n))$  время доступа к своим элементам. Другим недостатком является то,

что операции могут быть выполнены только над отдельными элементами массива, а не всей структурой целиком, из-за низкого уровня, на котором применяется модель секвенирования потока данных. Поэтому, выполнение двух независящих друг от друга операций над массивами все равно будет осуществлено последовательно. Структуры с таким поведением называют *ограниченными* или *прямолинейными*.

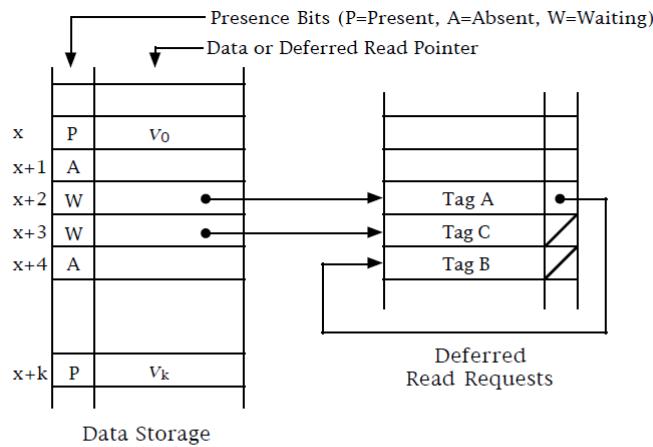

#### 1.2.4.3 I-структуры

I-структуры впервые были предложены Арвином и Томасом, в качестве основного механизма построения структур данных для потоковой архитектуры с тегированными токенами [21, 22]. I-структуры – это асинхронные структуры данных, которые ведут себя похожим образом с массивами. Отличительной особенностью рассматриваемой структуры данных является наличие ограничений на создание и доступ к ним. А именно, I-структура **создается ровно один раз** и каждый ее элемент может быть **записан ровно один раз**. Асинхронная природа структуры позволяет исполняемой программе пытаться получить доступ на чтение элементов до того, как они будут записаны. Структуры с таким поведением называются *неограниченными* или *непрямолинейными*. На рисунке 1.2 (рисунок 19 из [17]) приводится пример взаимодействия с I-структурой.

Использование I-структур по сравнению с древовидными структурами обеспечивает более высокую скорость доступа и более низкие накладные расходы по памяти, но в ряде случаев может плохо сочетаться с решаемой задачей.

Достигается асинхронное поведение за счет реализации концепции «потребление до завершения формирования». Для этого в состав элементов структуры данных вводят специальные биты, называемые *битами готовности*. Эти биты задают три допустимых состояния элемента структуры:

- PRESENT – означает, что данное присутствует в ячейке памяти и может быть считано;

- ABSENT – означает, что записи в данную ячейку памяти не производилось с момента ее выделения и попыток чтения не было;

- WAITING - означает, что записи в данную ячейку памяти не производилось с момента ее выделения, но попытки чтения были. В этом состоянии запросы на чтение откладываются в специальный связный список из *deferred read* запросов.

Данный подход был разработан в процессе улучшения базовой Манчестерской машины и был назван Extended MANchester (EXMAN) computer [23]. Данная машина снижает избыточность памяти путем хранения в токенах указателя на начало массива и увеличивает скорость доступа за счет использования традиционных структур со случайным доступом. Исходный массив данных хранится последовательным образом в виде структуры со случайным константным временем доступа.

A sequence of operations producing this structure:

- Attempt to READ(x+2) for instruction A

- WRITE(x+k)

- Attempt to READ(x+3) for instruction C

- WRITE(x)

- Attempt to READ(x+2) for instruction B

- READ(x)

Рисунок 1.2 – Пример I-структур (рис. 19 из [17])

#### 1.2.4.4 Усовершенствованный Манчестеровский подход

Чтобы выполнить операцию APPEND, создается новый узел, который содержит новое значение тегированного токена и модифицируемый индекс. Таким образом, для корректного выполнения операцию APPEND необходимо снабдить тремя аргументами: ссылкой на массив, индексом обновляемого элемента и значением. Последовательность операций APPEND над массивом формируют структуру связного списка из новых элементов.

Операция SELECT снабжается двумя аргументами: ссылкой на структуру данных; индексом считываемого элемента. Выполнение операции SELECT осуществляется путем обхода сперва связного списка модифицированных элементов. В случае, если в ходе обхода в списке находится совпадающий индекс, возвращается соответствующее значение. Иначе, данное считывается из исходного массива по заданному индексу.

Таким образом, подход EXMAN избегает излишнего копирования за счет совместного использования динамических указателей и структур данных с константным случайным доступом. Это позволяет снизить накладные расходы по памяти. Однако, по мере роста числа измененных элементов, скорость выполнения операции SELECT будет снижаться, значительно уменьшая производительность.

#### 1.2.4.5 Гибридная схема

Гибридная схема формирования структур данных была предложена Ли и Харсоном [24]. Основная идея данной схемы заключается в сопоставлении концептуальному массиву специальный шаблон, называемый *структурный шаблон*. Это позволят минимизировать

копирование за счет размещения в новом массиве только измененных элементов. Каждый массив представляется *гибридной структурой*, которая состоит из структурного шаблона и вектора элементов массива. Гибридная схема хорошо сочетается с I-структурами.

Существует проблема выполнения операции APPEND. Выполнение данной операции приводит к созданию абсолютно нового массива. Это является удовлетворительным поведением в случае, если: размер массива небольшой или выполняемая программа подразумевает обновление всех элементов массива. Далеко не всегда эти условия выполняются. Поэтому гибридная схема позволяет разбивать большие массивы на множество более мелких массивов, каждый из которых интерпретируется как гибридная схема. С помощью таблицы доступа все небольшие массивы связываются в единую структуру данных. Это обеспечивает константное время доступа ко всем элементам.

### 1.2.5 Балансировка вычислительной нагрузки

Существует две основные проблемы распределения вычислительной нагрузки, которые могут быть обозначены как *разбиение и назначение* [25]. Разбиение – это деление алгоритма на процедуры, модули и процессы. Назначение – это распределение, полученных в ходе разбиения элементов, по процессорам. Конечная цель заключается в разработке схемы эффективной балансировки нагрузки, которая будет избегать конкуренции между процессорами и уменьшать взаимодействия в коммуникационной среде. Однако обе указанные задачи находятся в прямом конфликте между собой, что делает решение данной проблемы нетривиальным [17]. Поэтому, создание единственной схемы балансировки нагрузки, которая смогла бы покрыть широкий спектр потоковых архитектур – чрезвычайно сложная задача. В работе [25] рассматриваются два основных подхода балансировки подзадач потокового графа: статический и динамический.

При статической балансировке нагрузки задачи распределяются на этапе компиляции за счет использования глобальной информации о структуре вычислительной системы и исполняемой программы. Эта процедура выполняется один раз. Главным недостатком статической балансировки является ее неэффективность в случае, если оценка характеристик времени исполнения неточна или некорректна.

С другой стороны, динамическая балансировка нагрузки основана на измерениях загрузки процессоров в реальном масштабе времени в зависимости от поведения программы. Назначение задач происходит для самых низко нагруженных процессоров. Основным недостатком динамической схемы является существенная избыточность, связанная с оценкой степени загруженности процессоров и распределением задач в реальном времени.

Ранее было отмечено, что задача эффективной балансировки нагрузки является НР-полной. Поэтому был разработан ряд эвристических алгоритмов, основанных на планировании списка критических путей [24]. Основной идеей данного алгоритма является разбиение

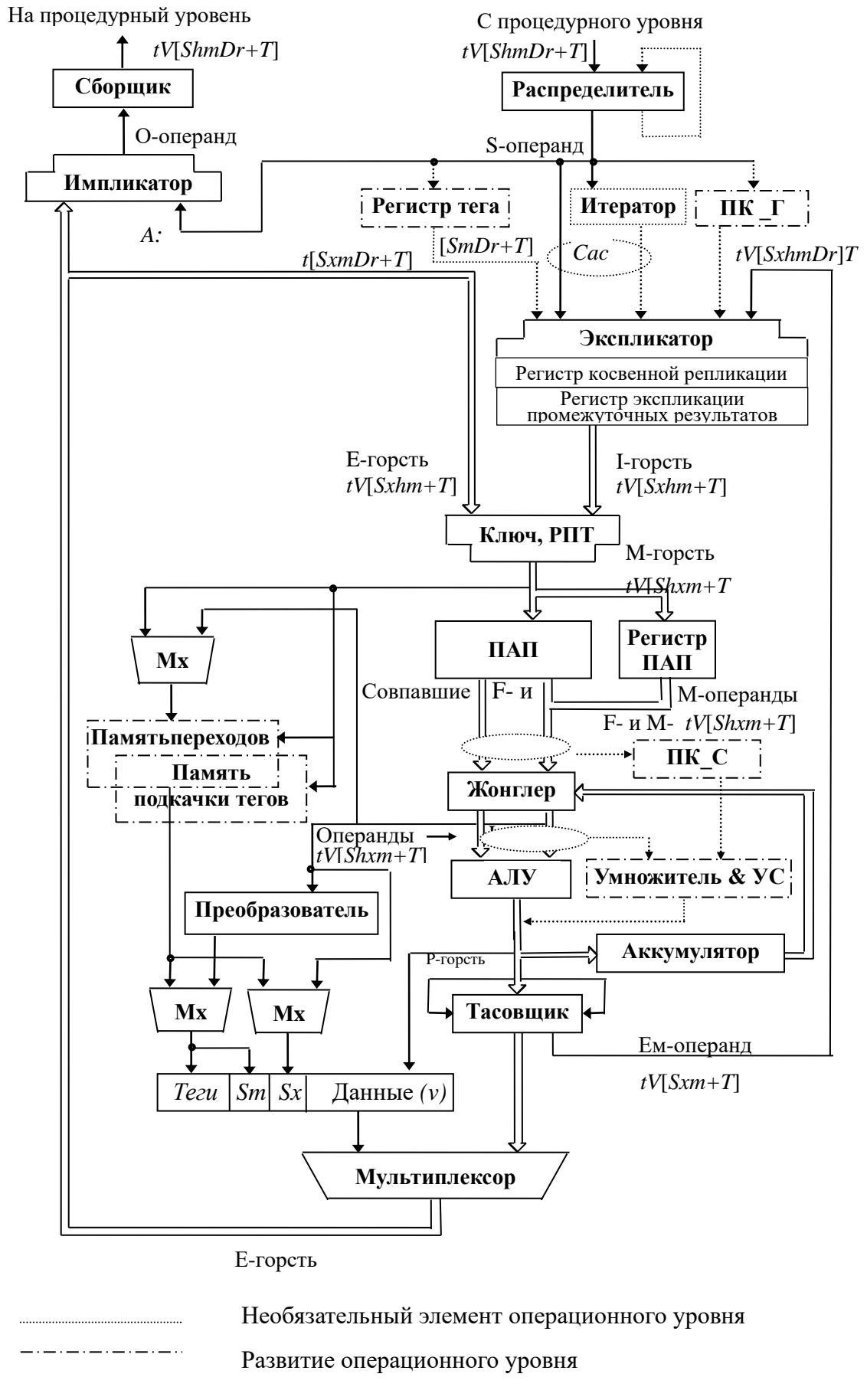

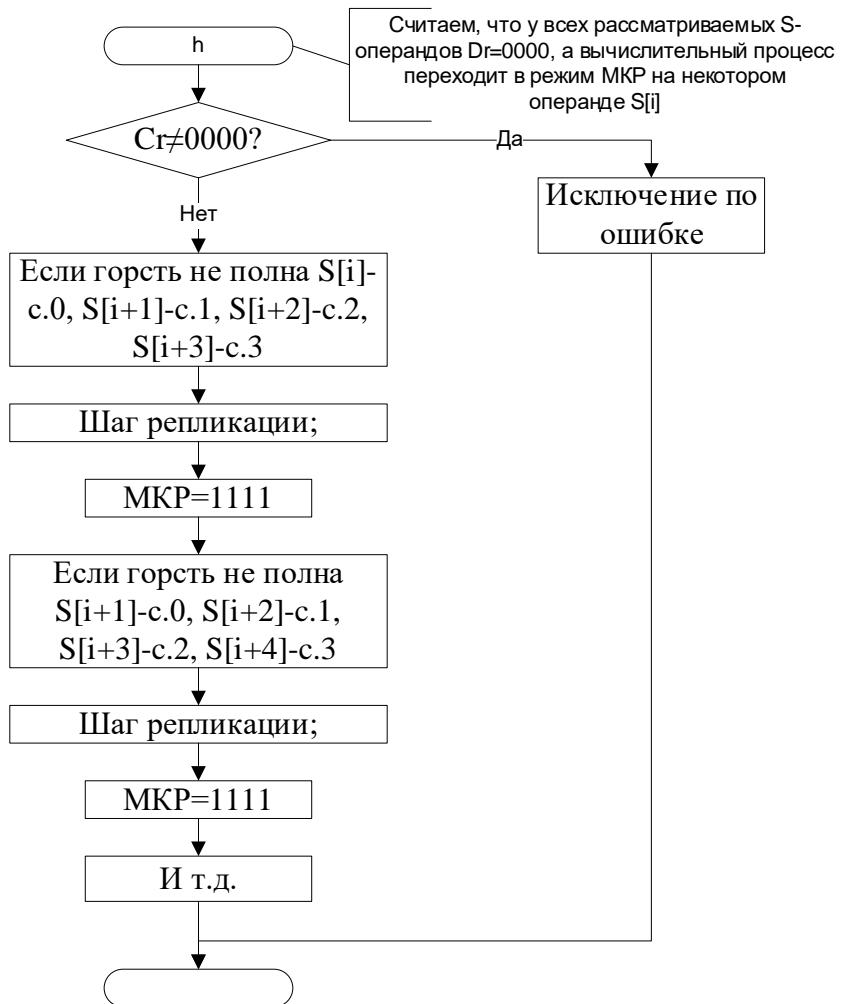

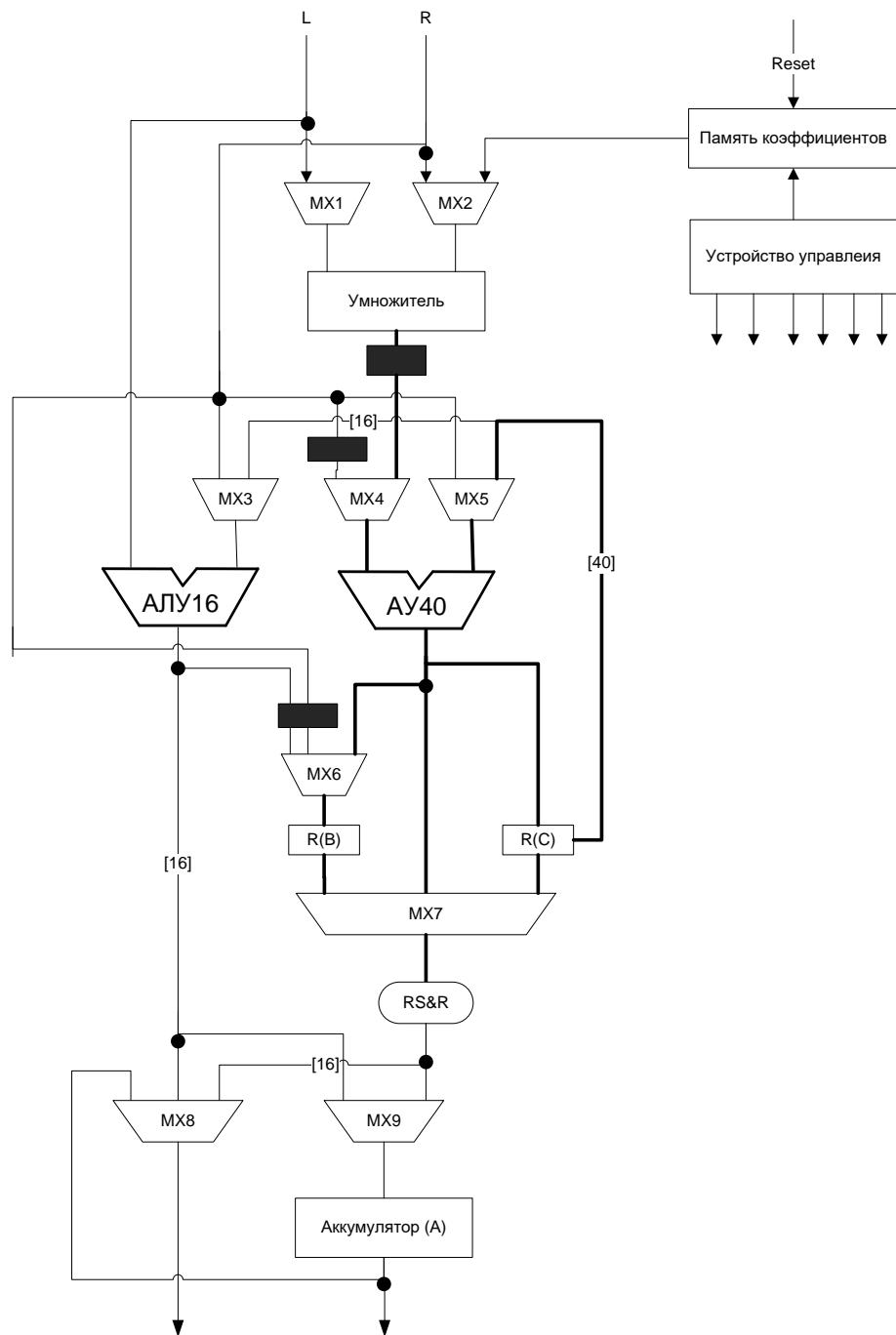

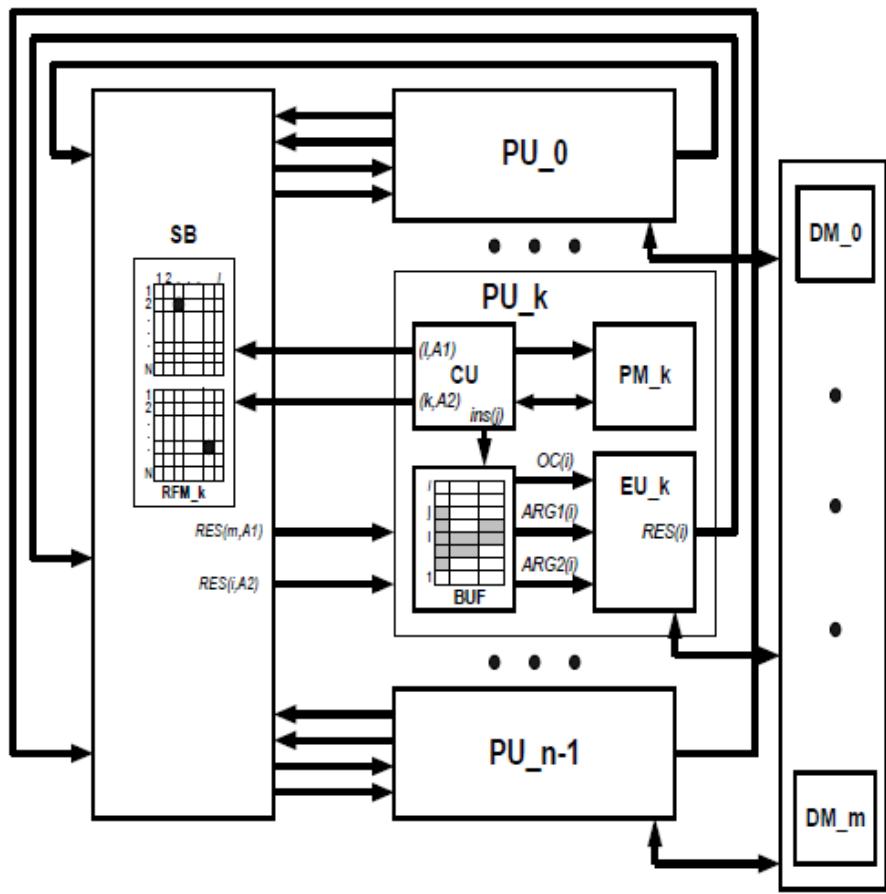

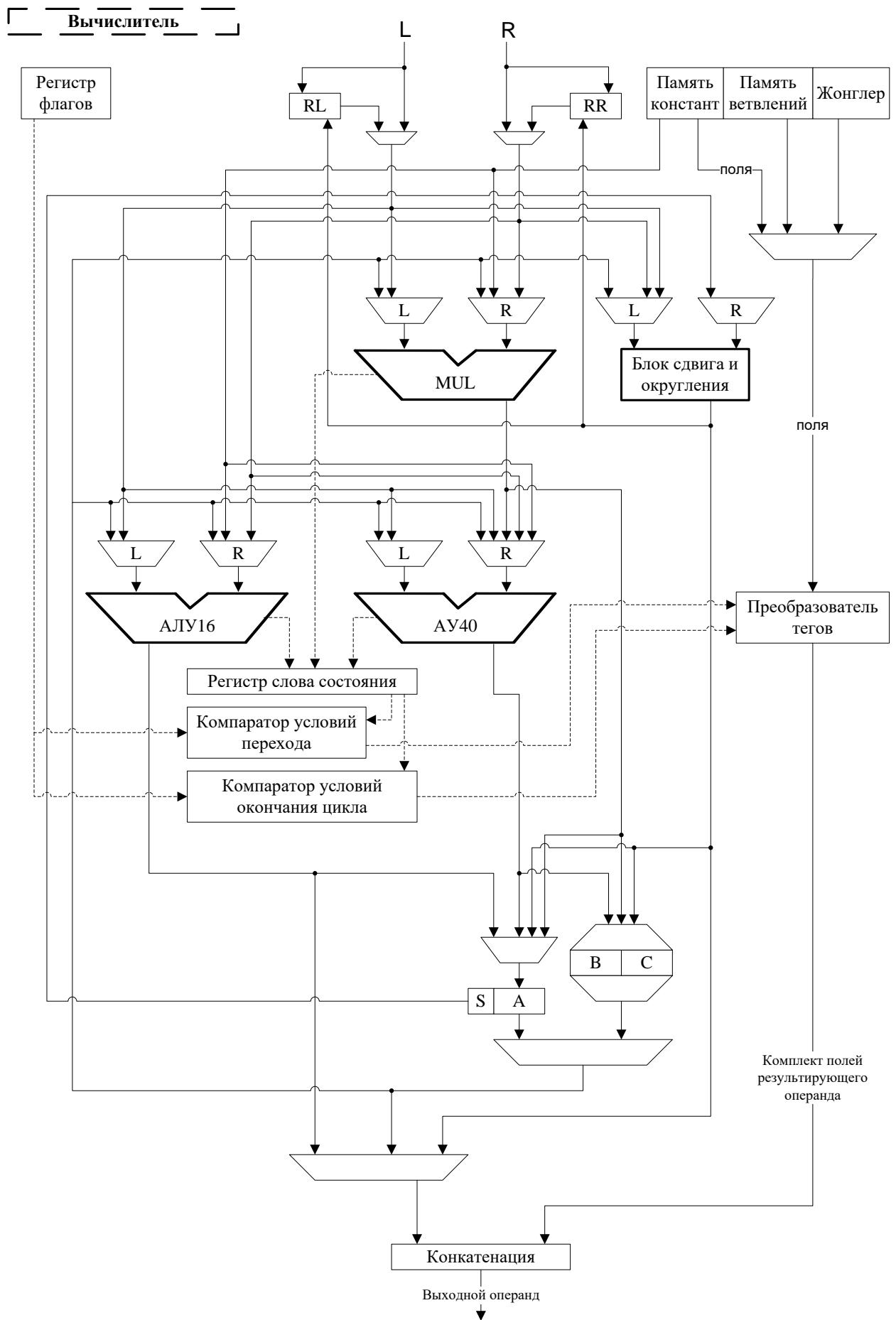

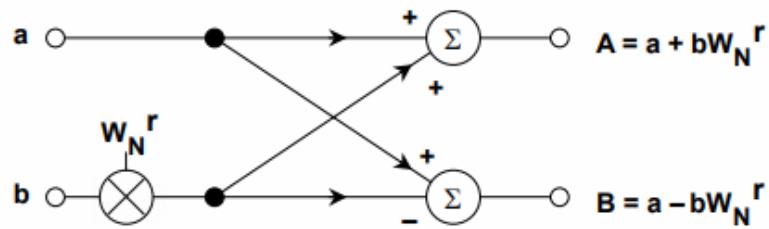

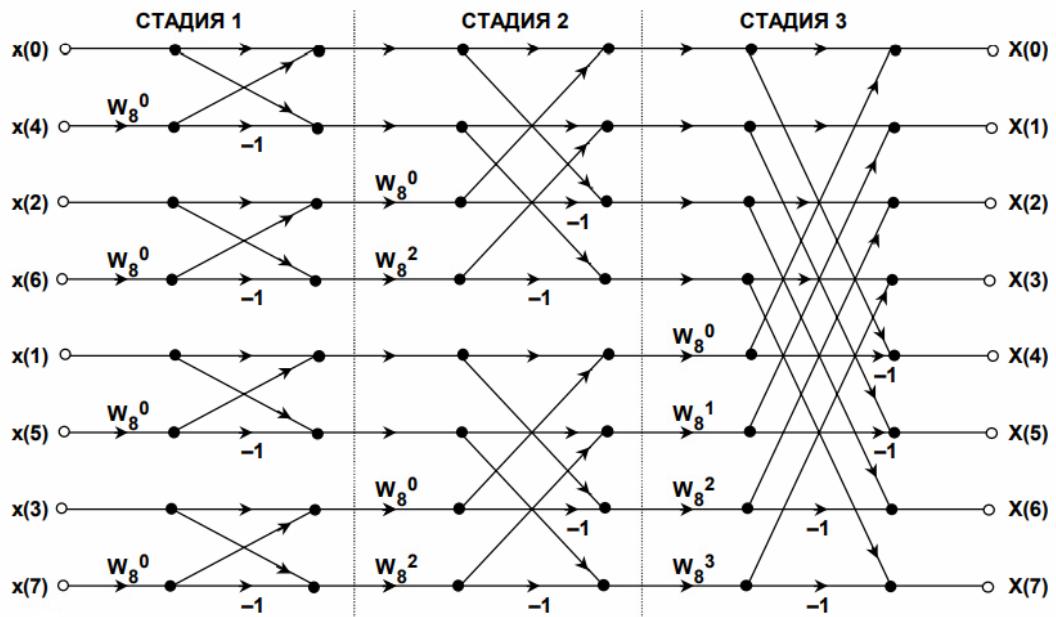

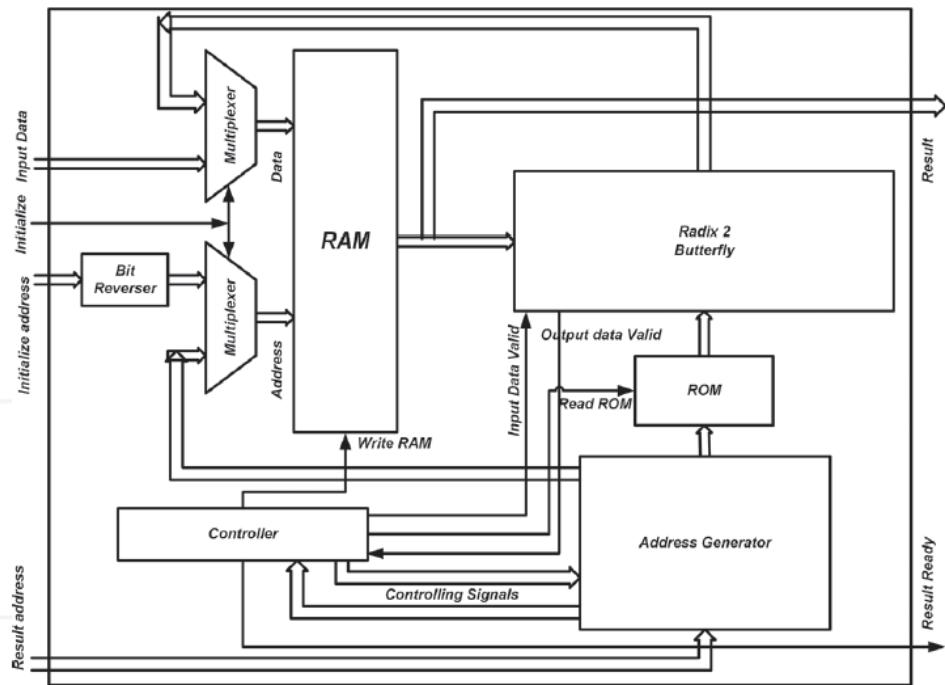

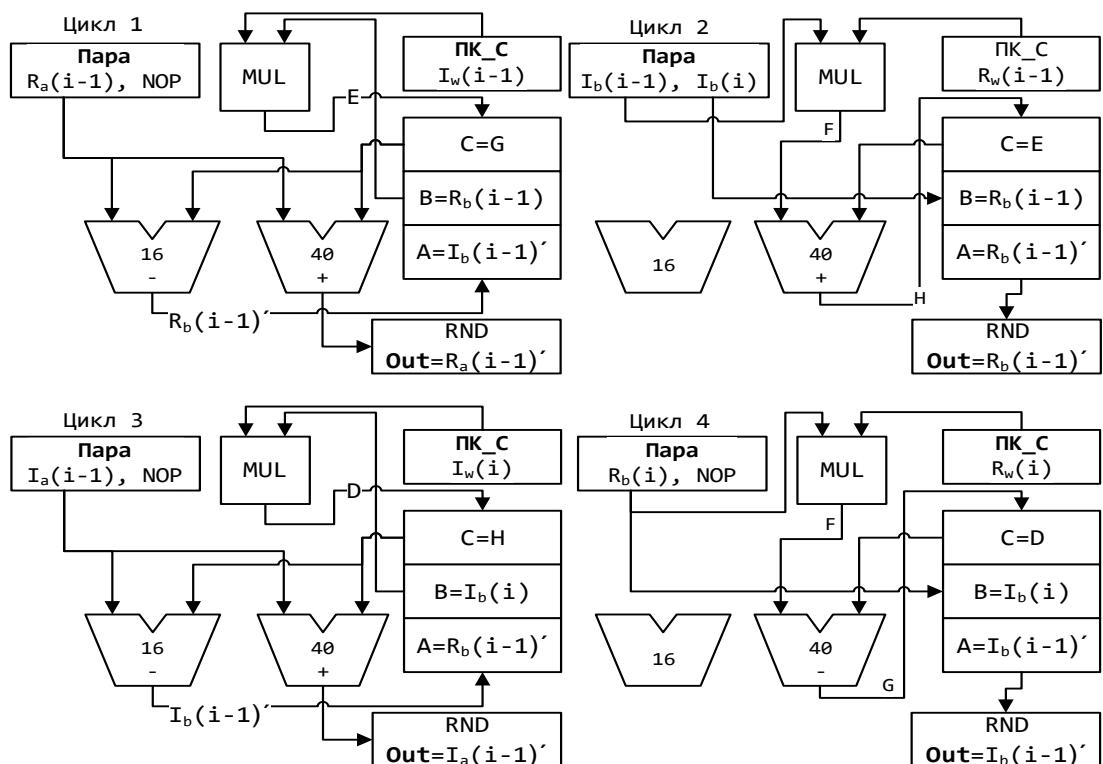

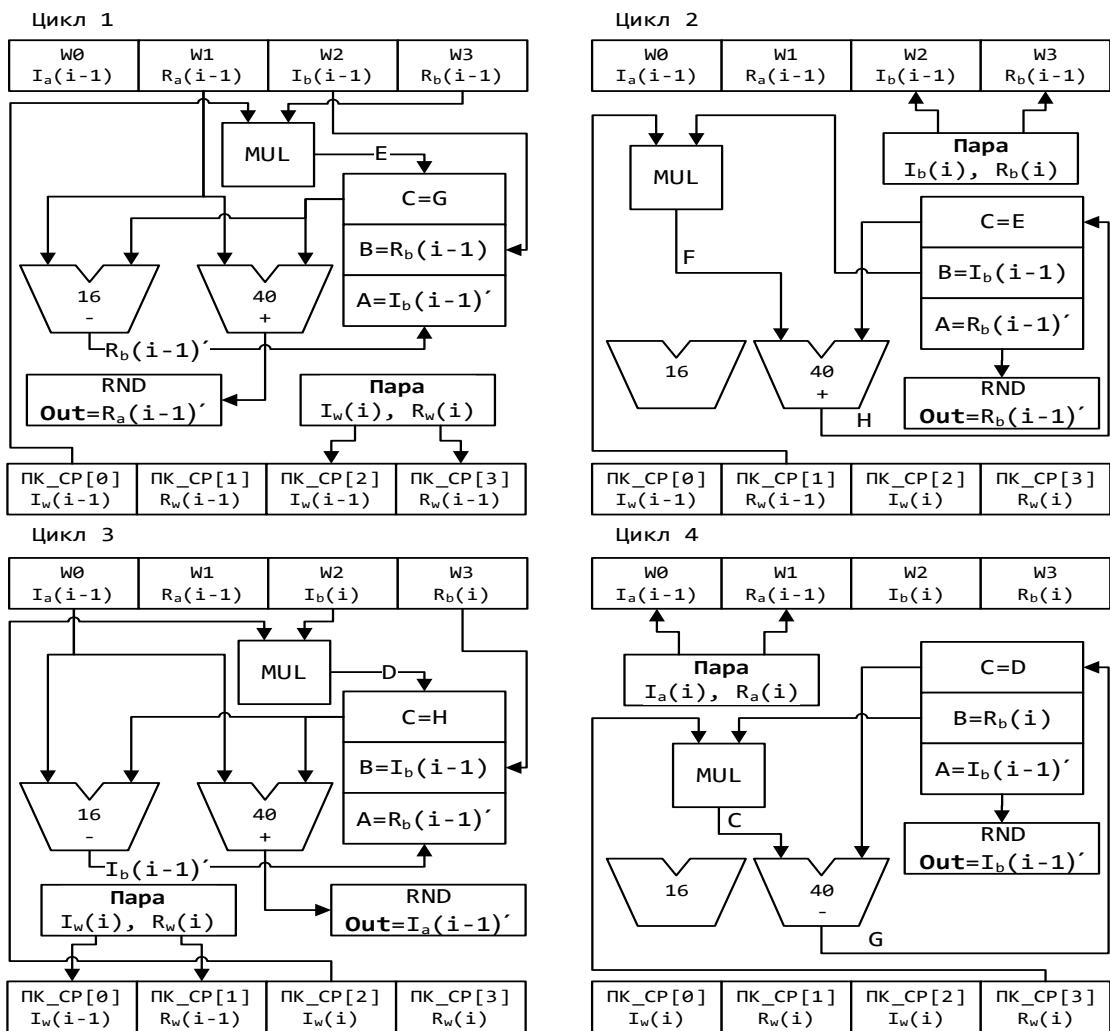

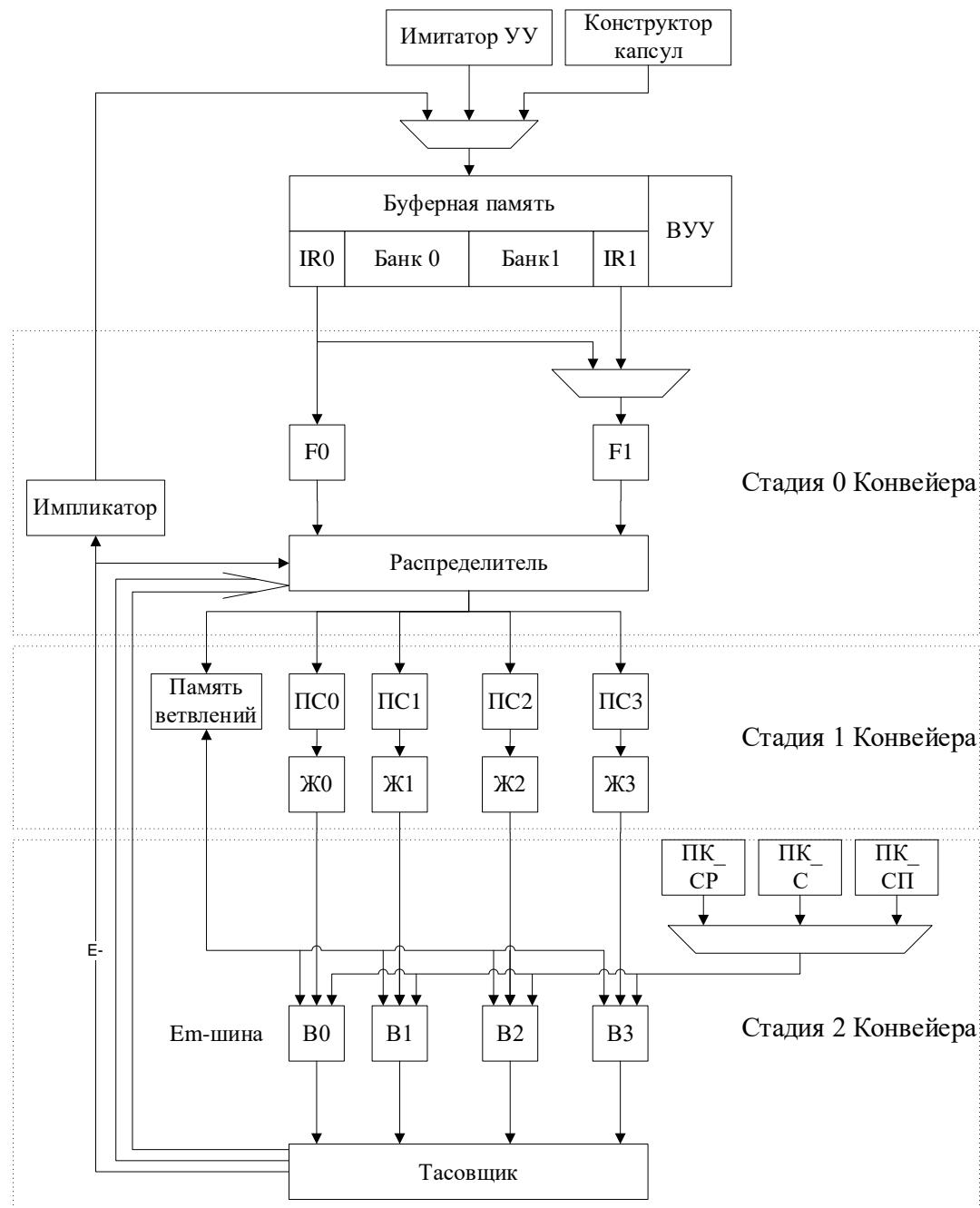

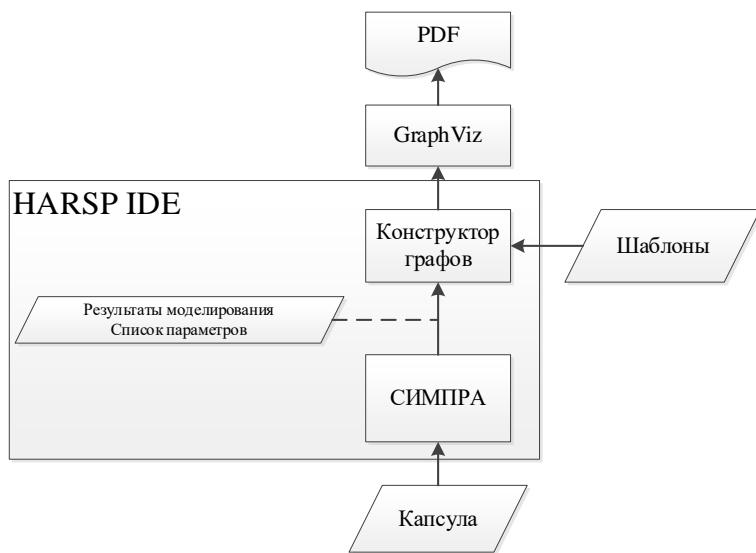

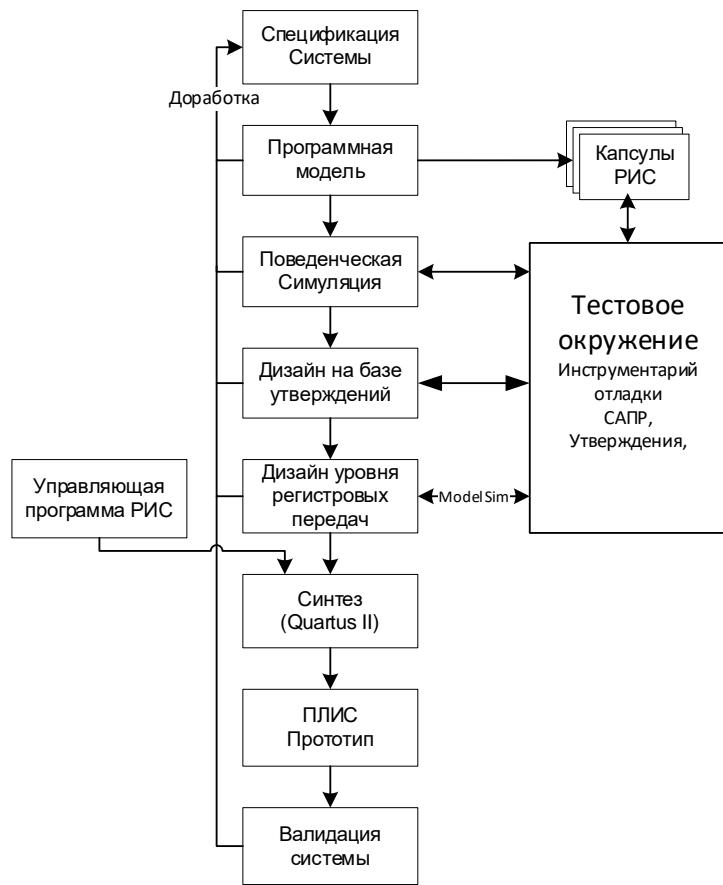

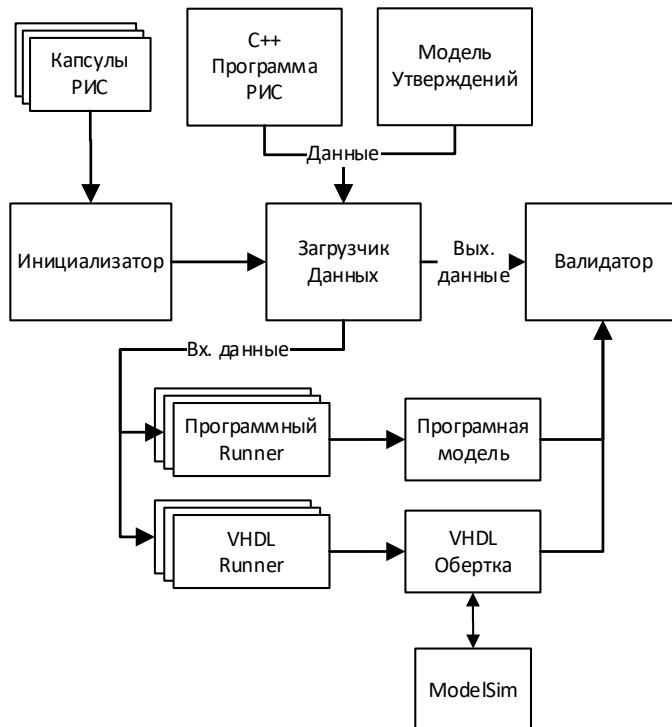

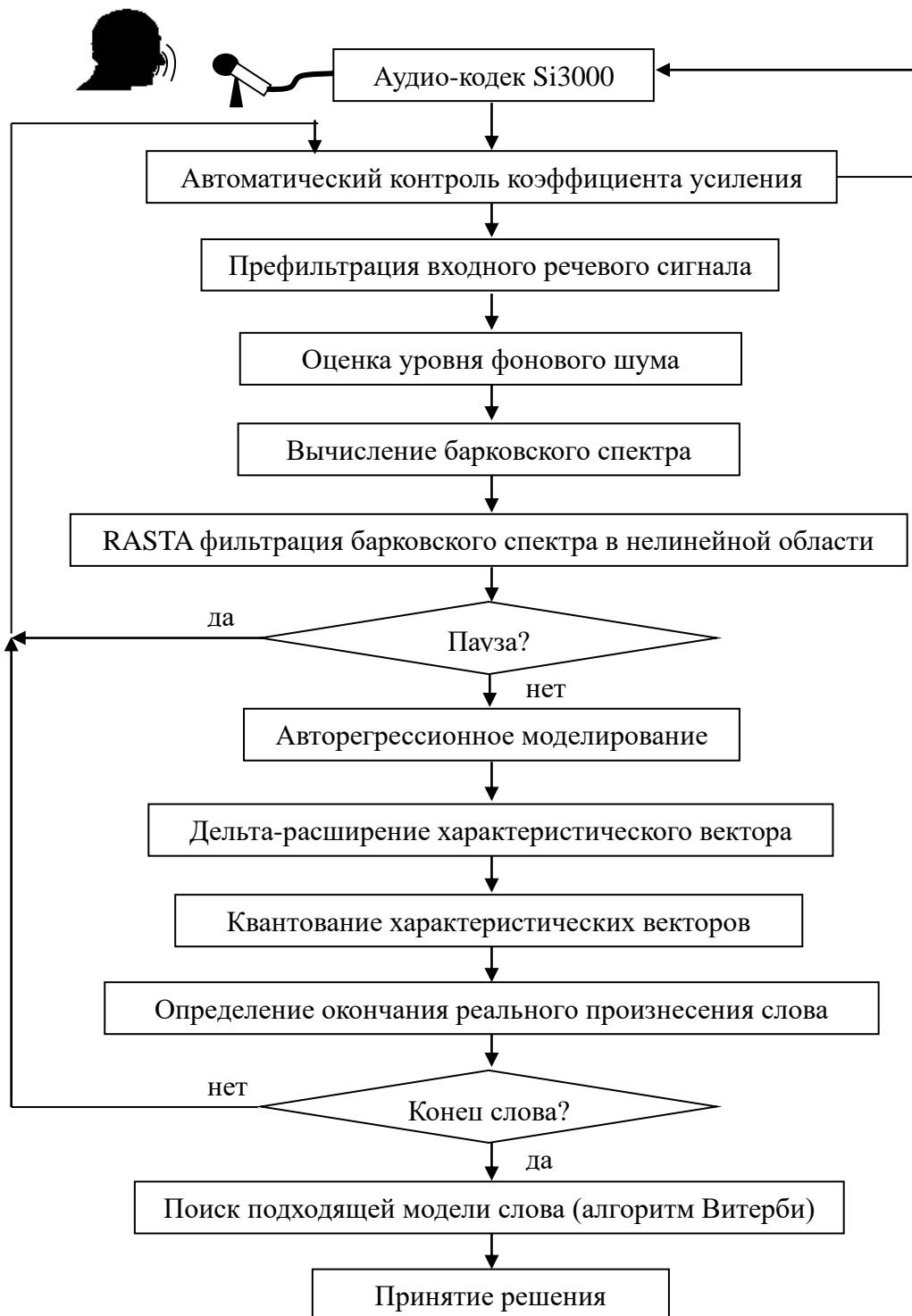

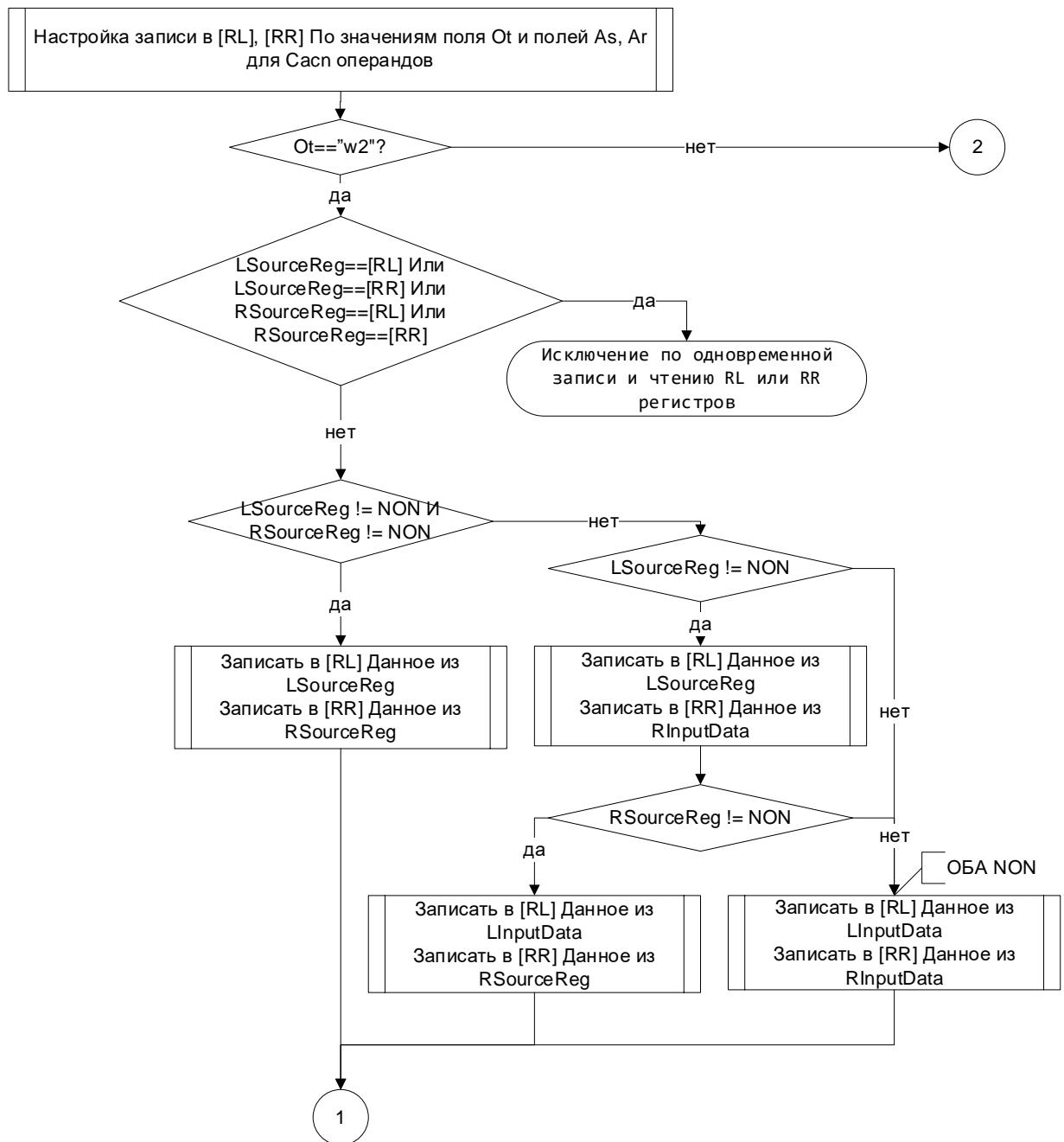

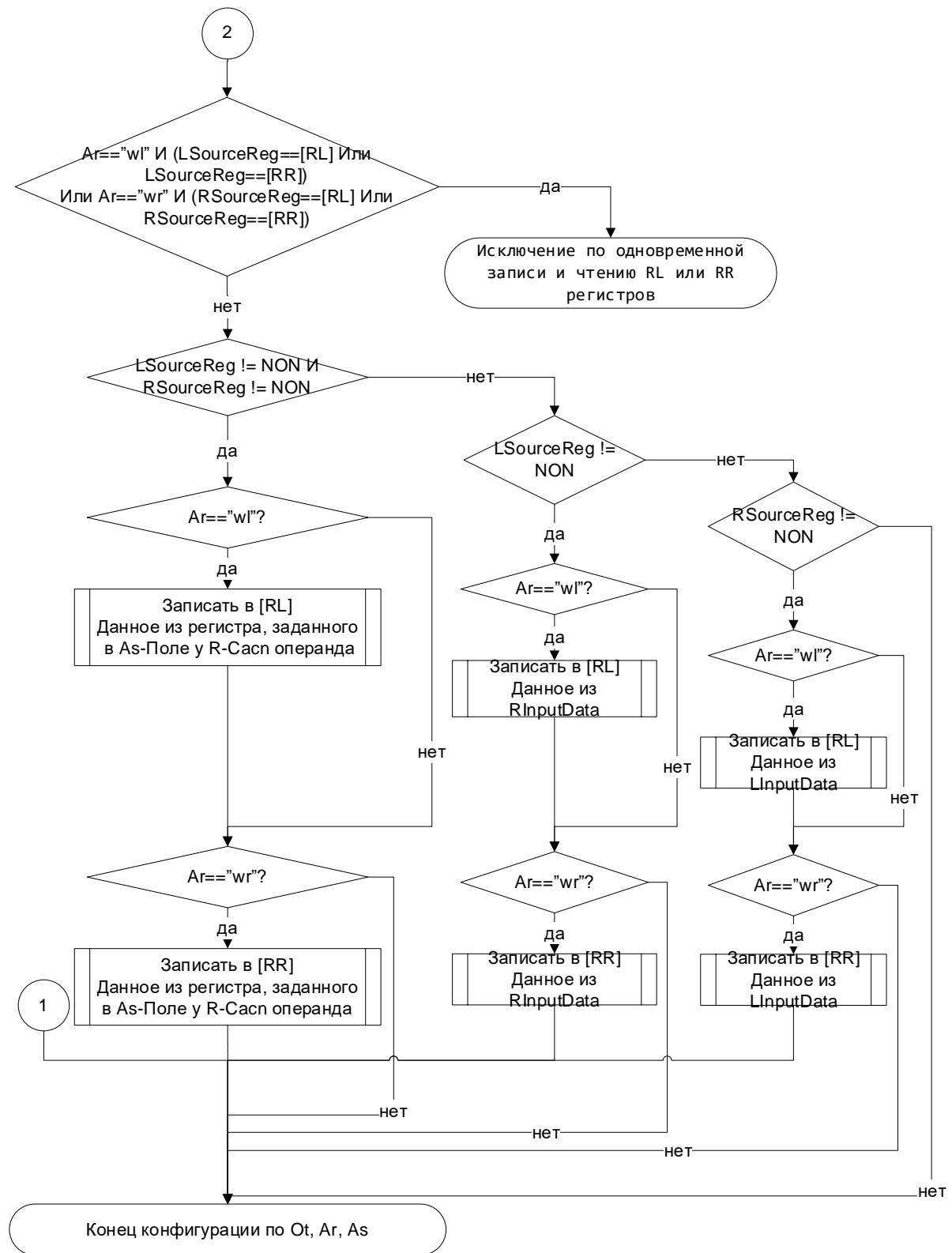

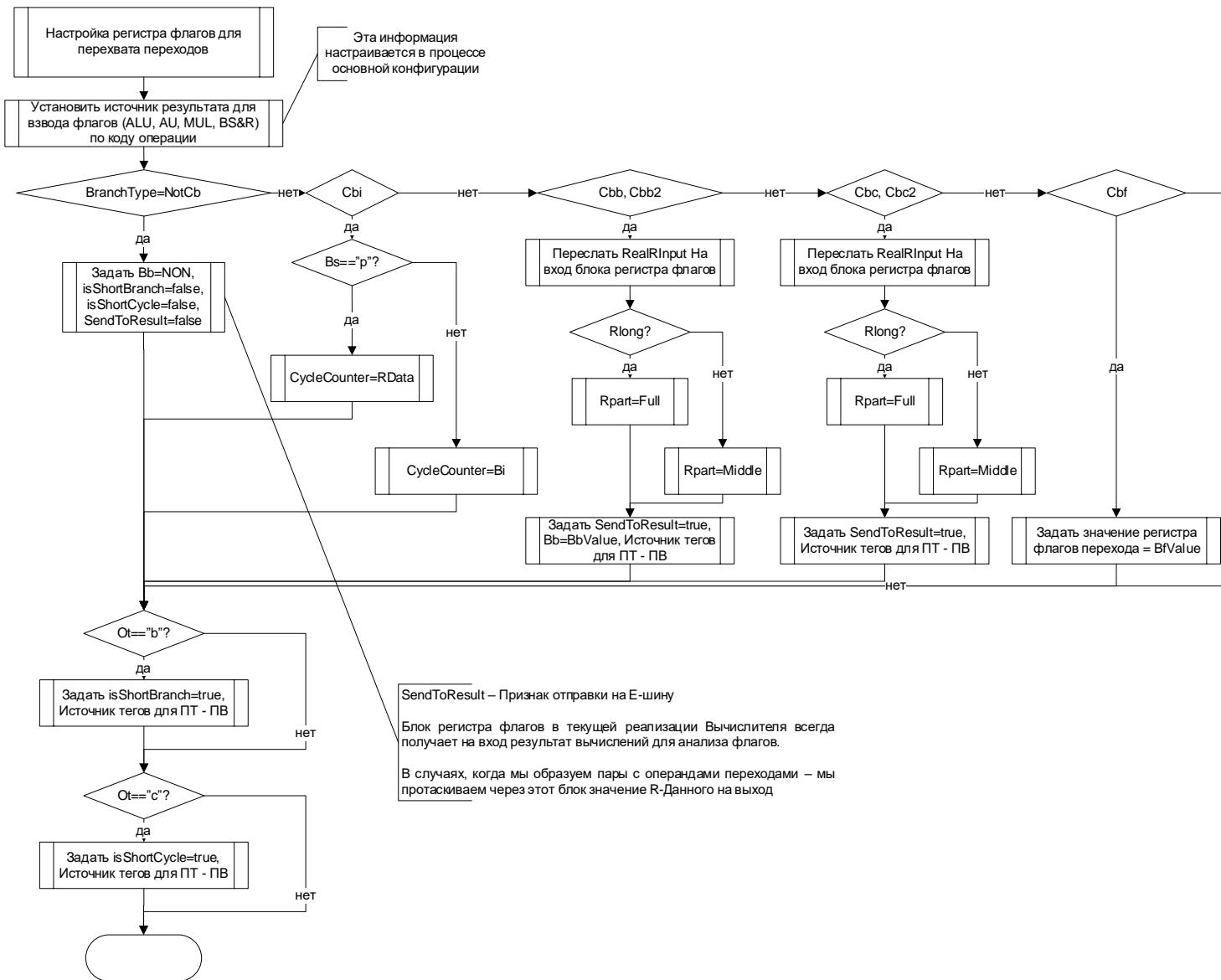

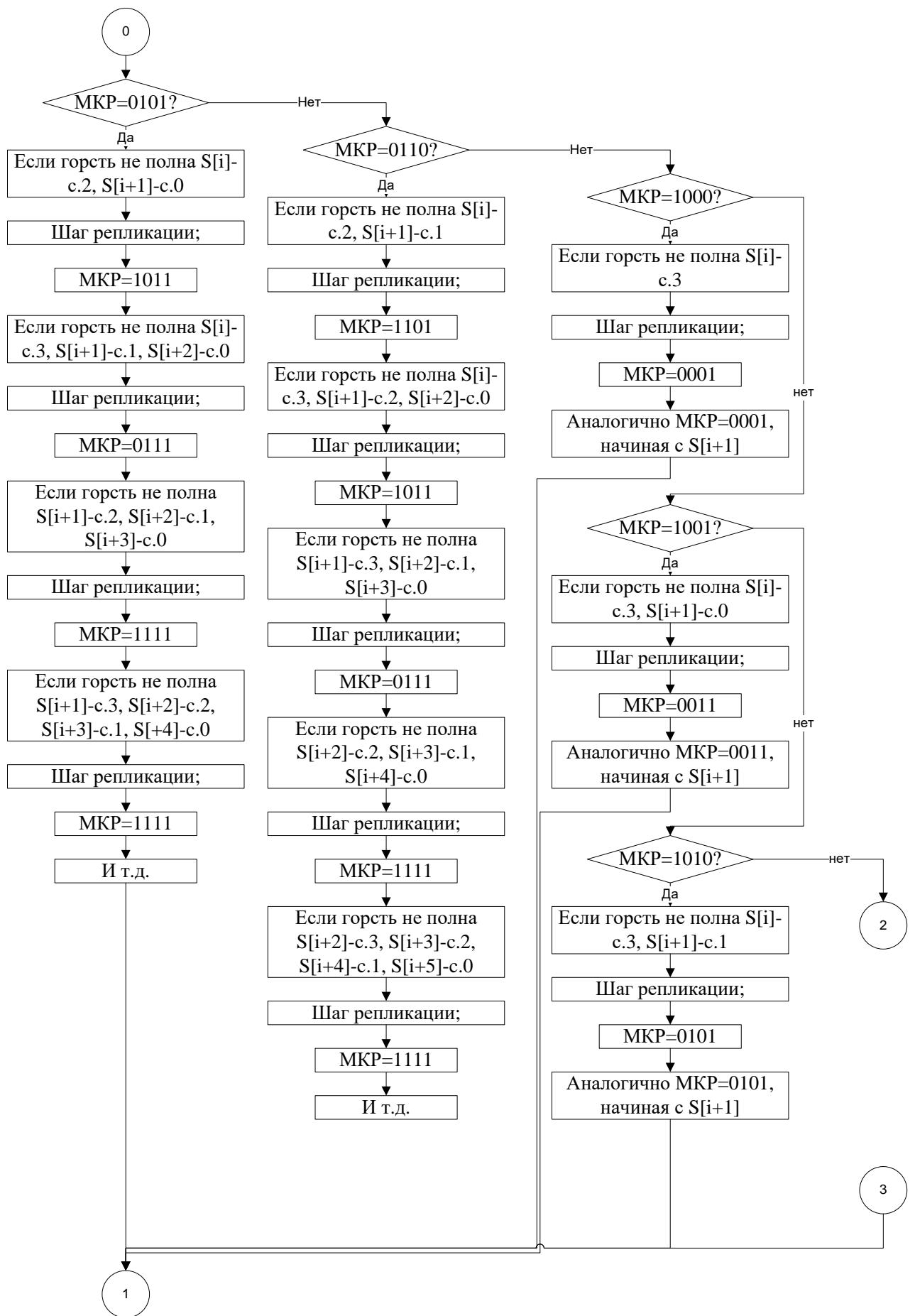

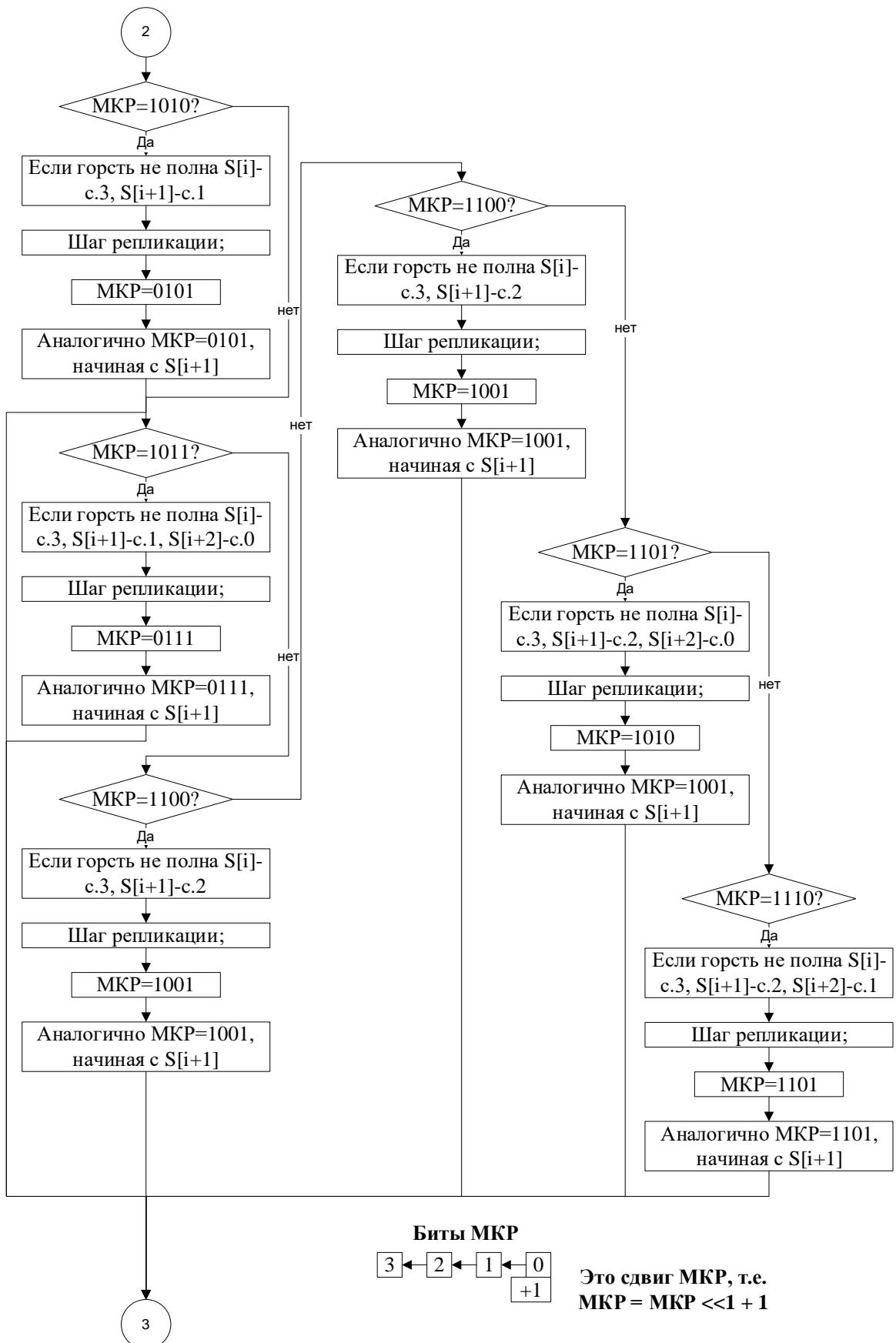

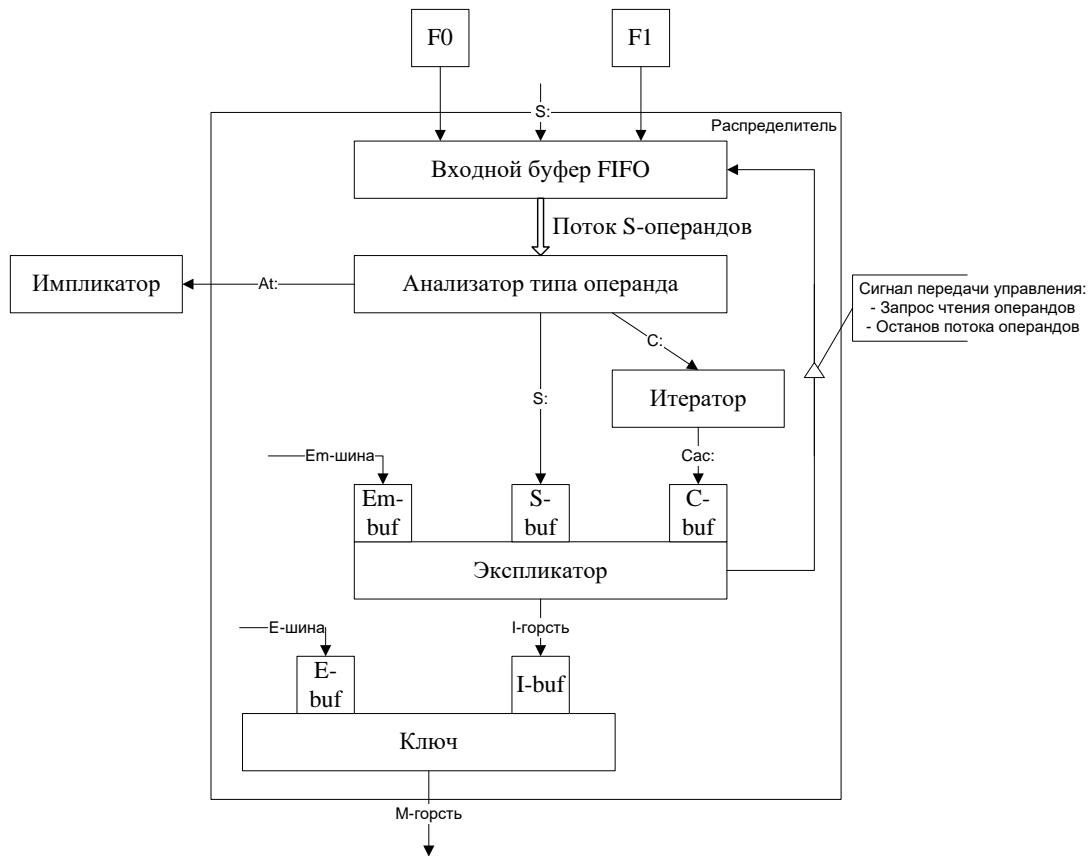

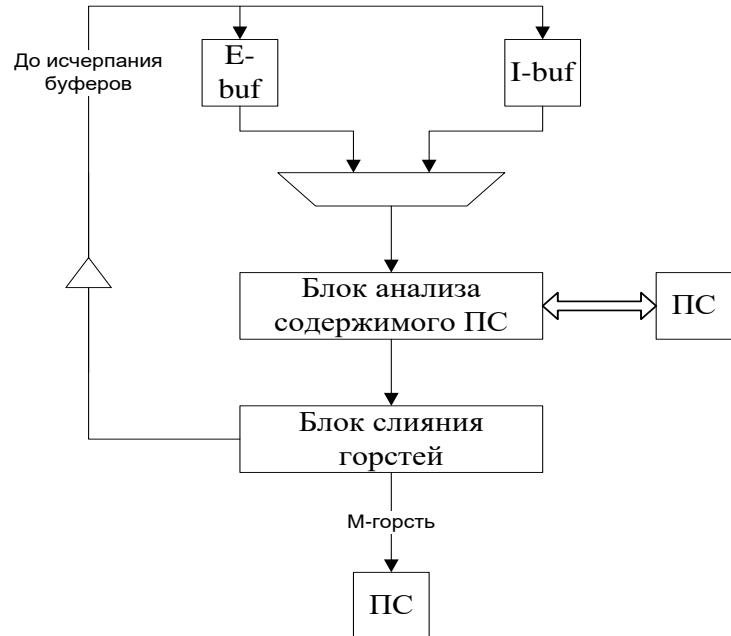

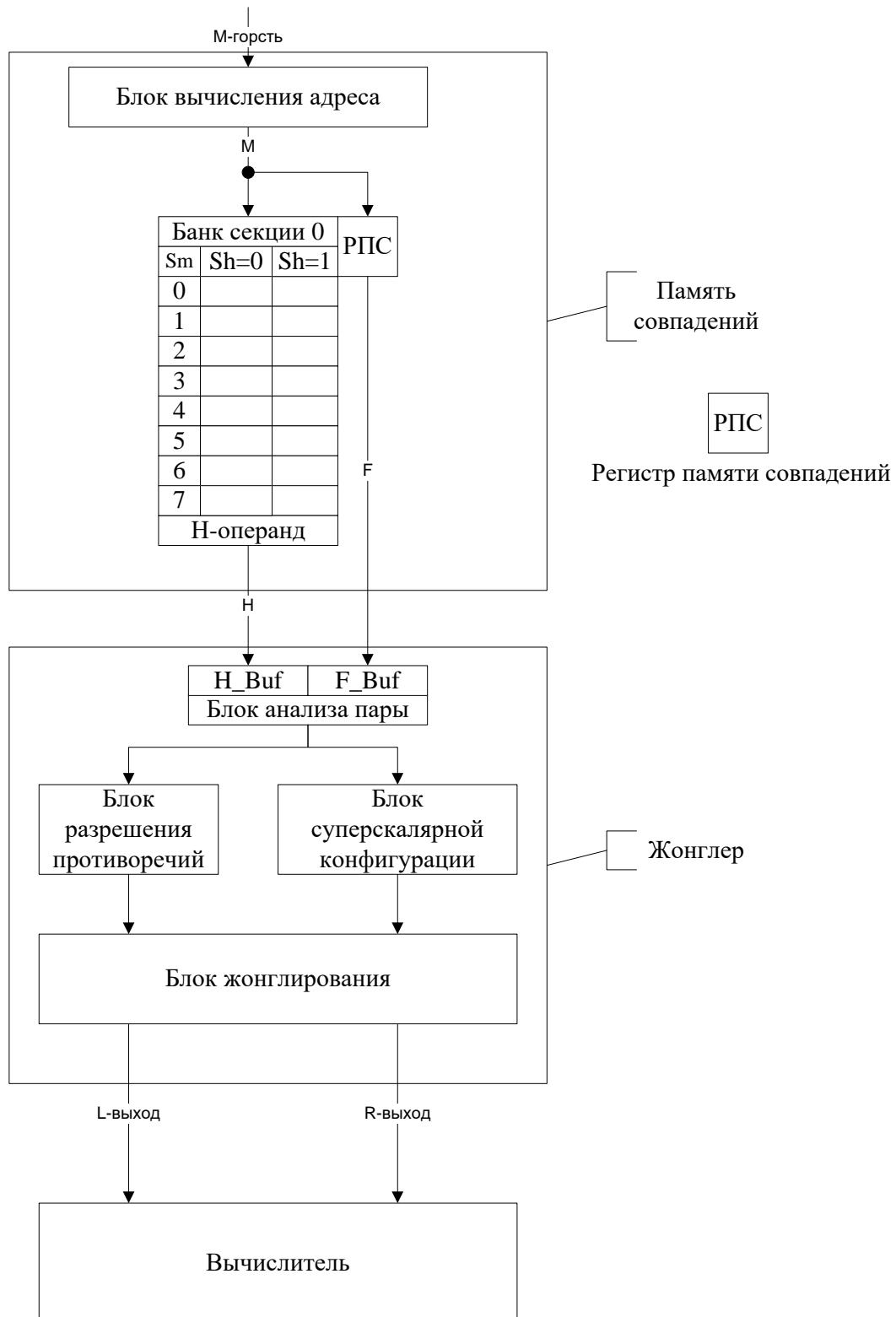

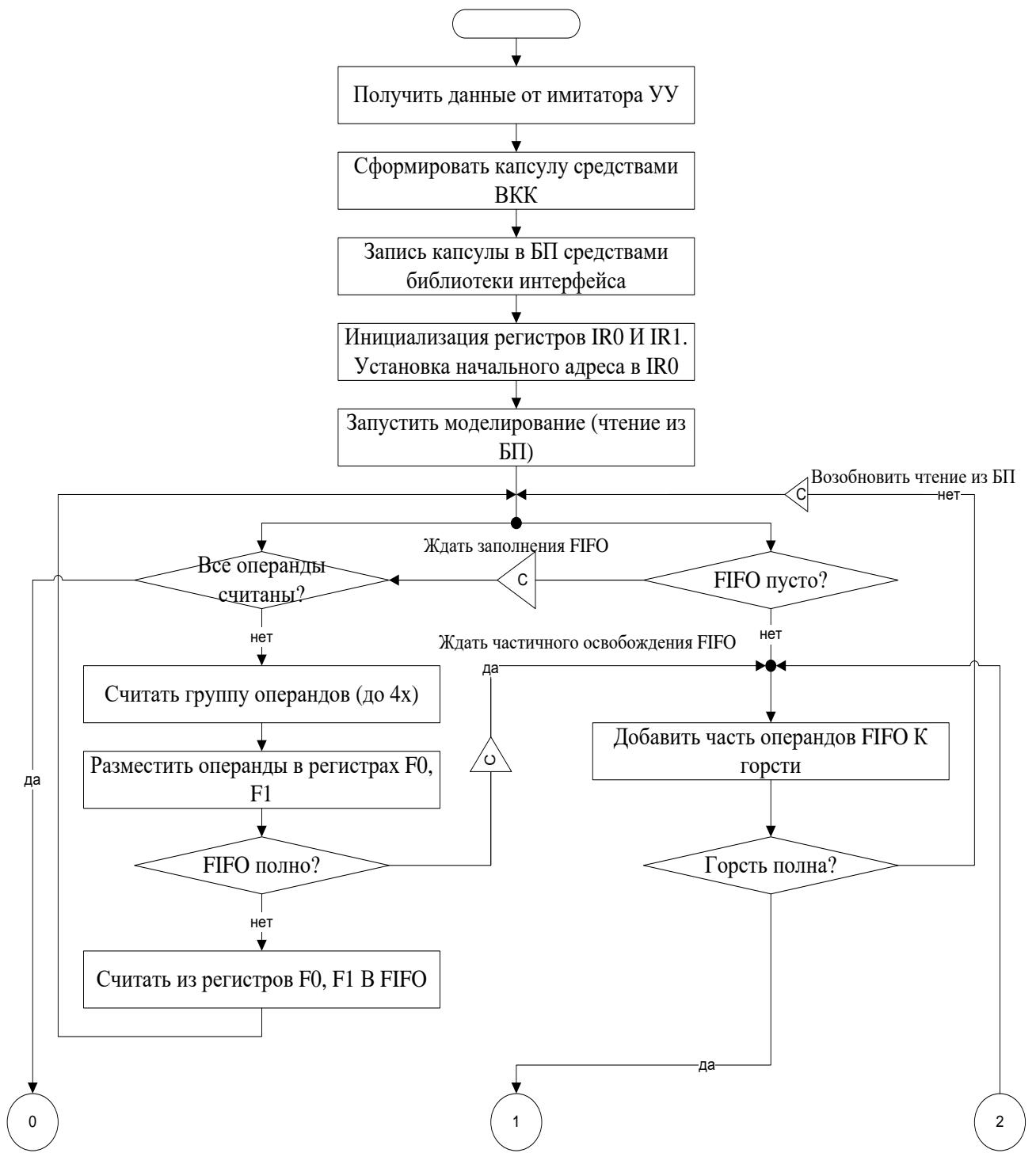

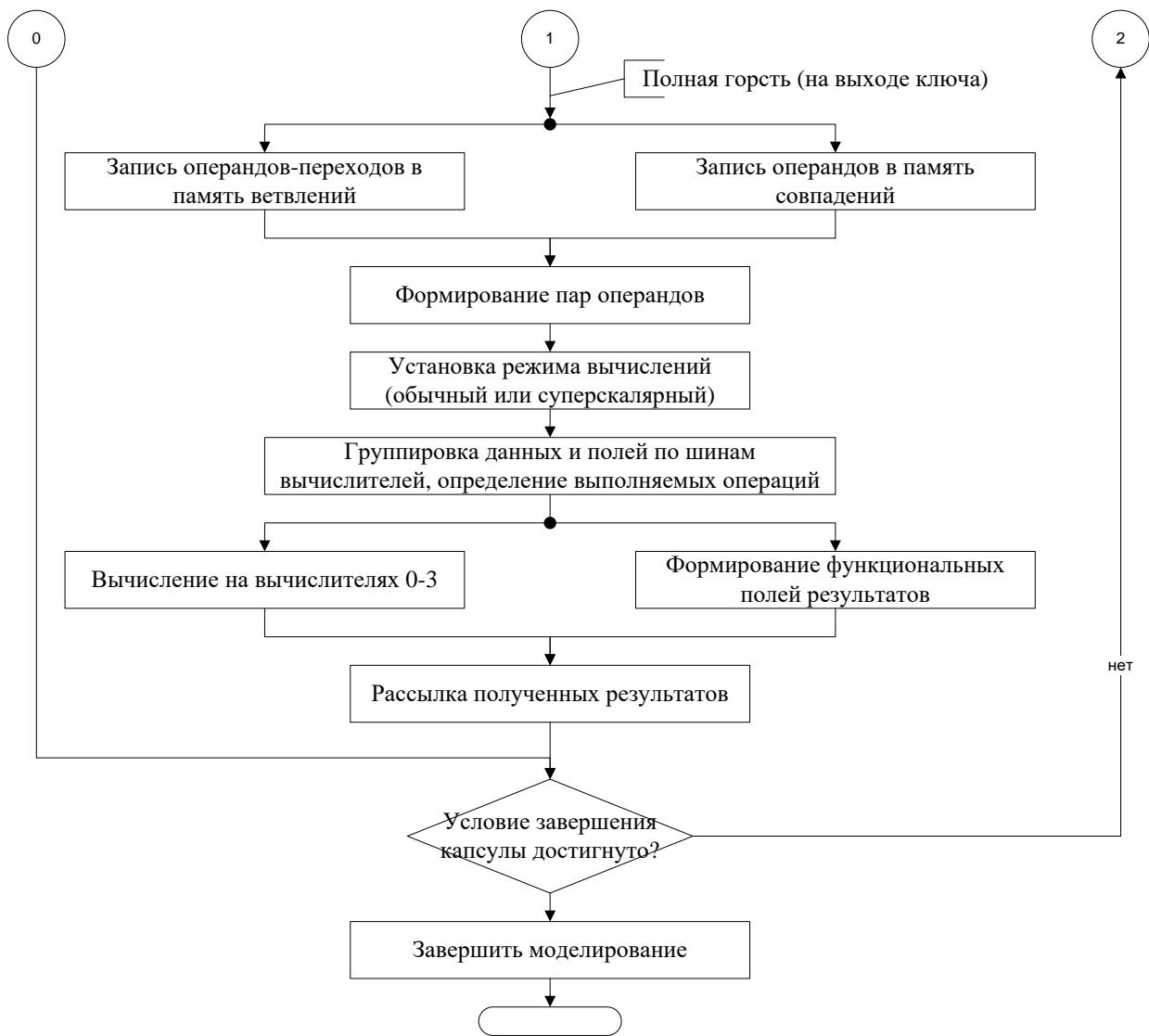

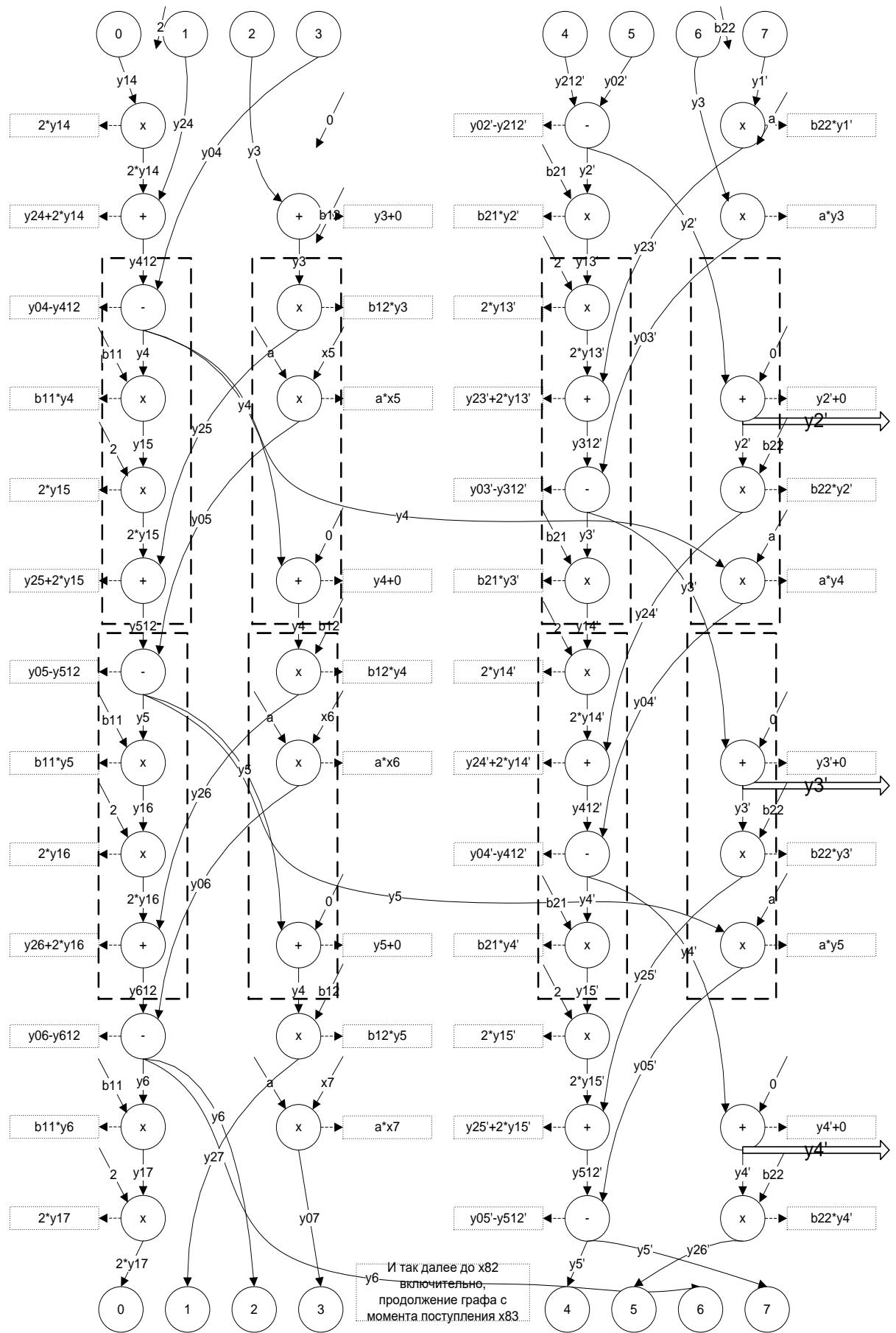

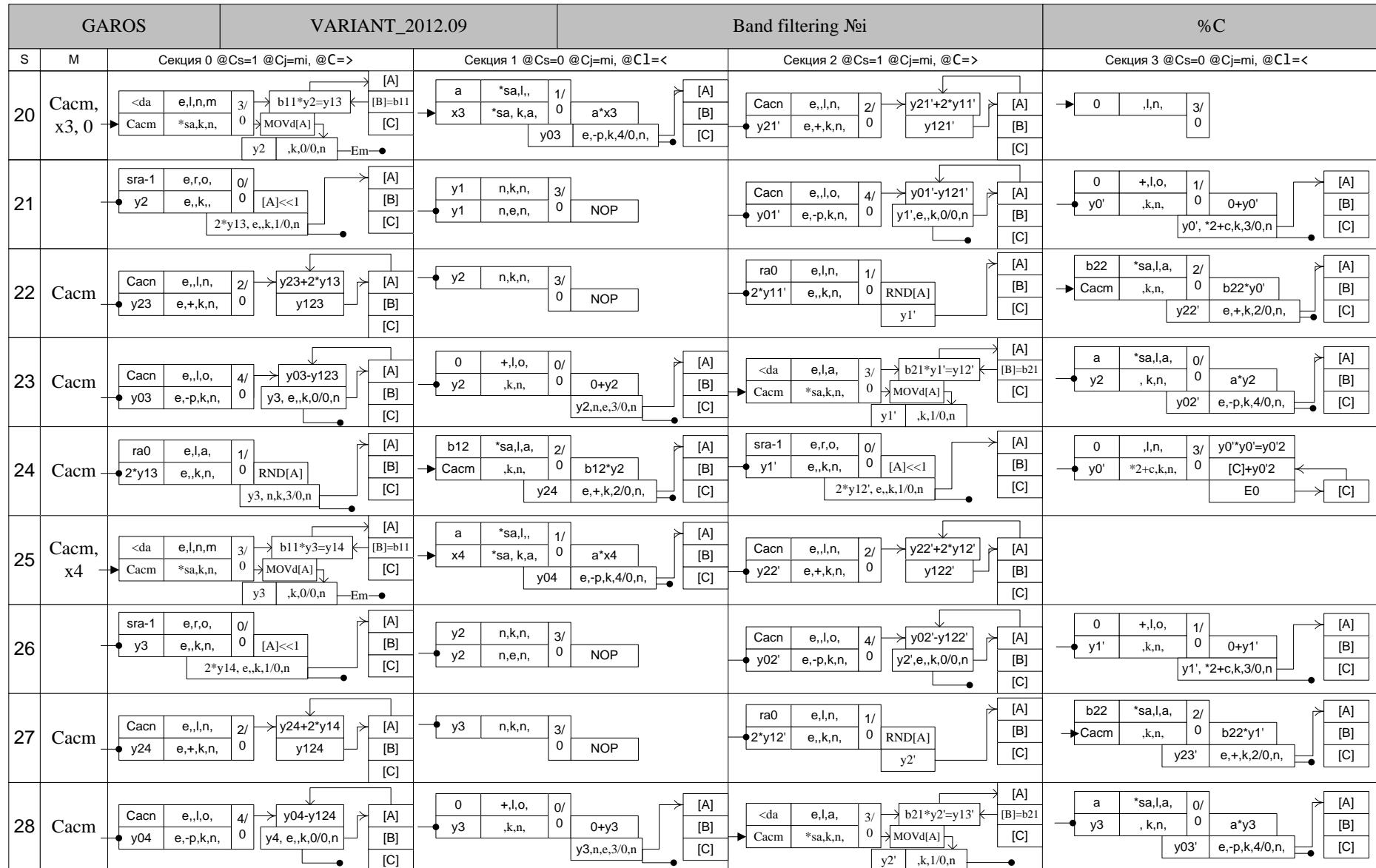

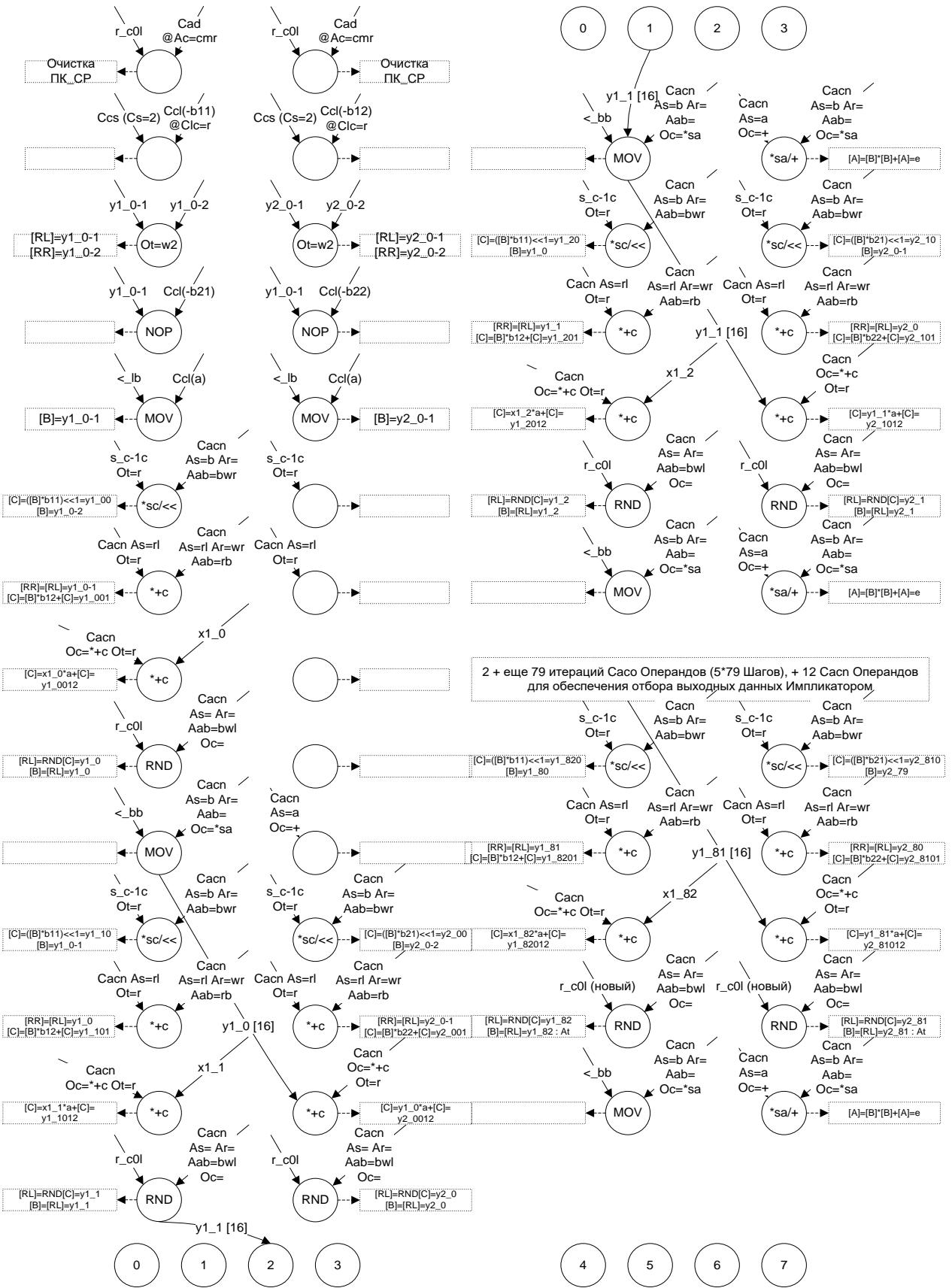

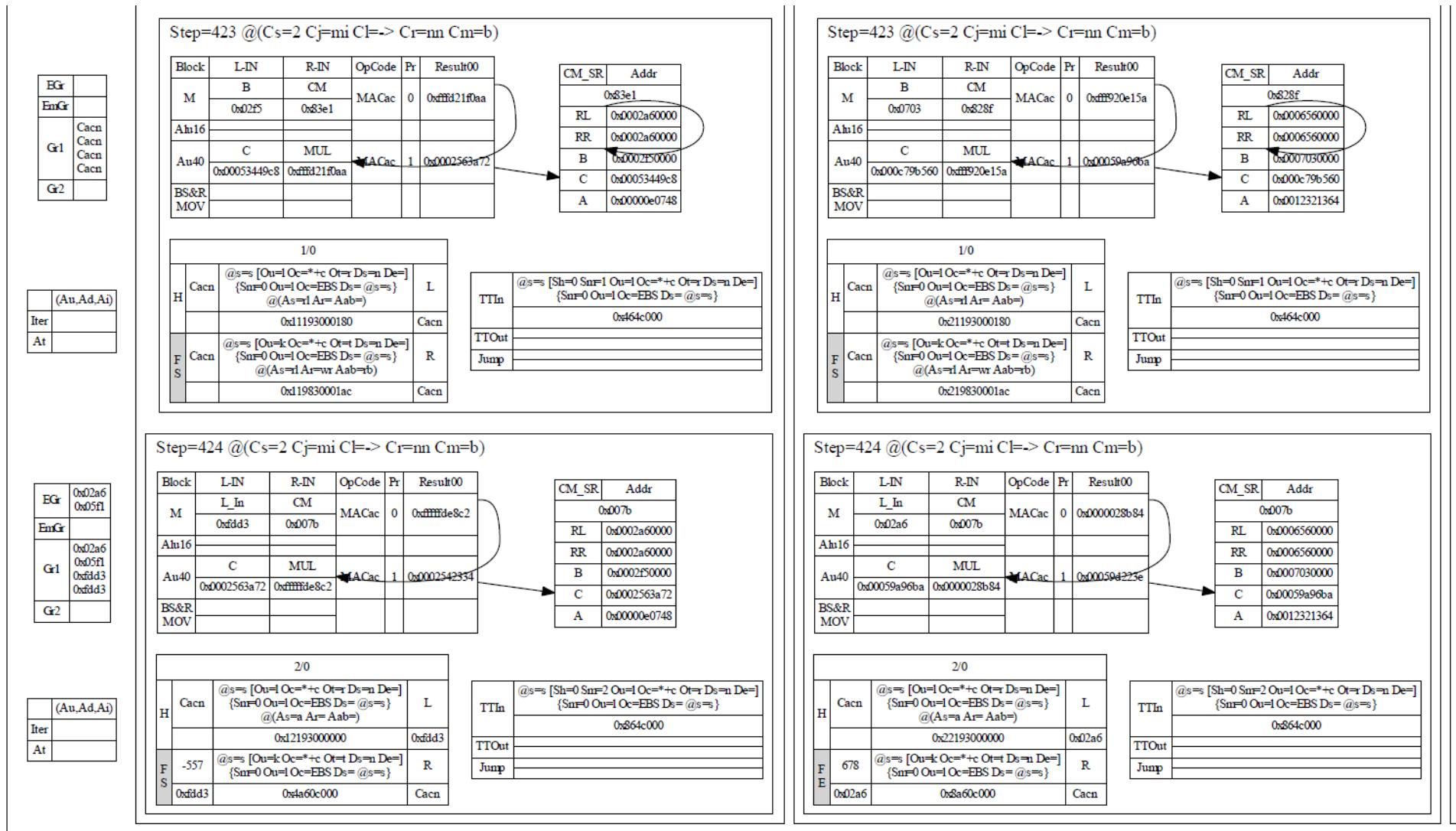

потокового графа на множество линейных подграфов, которые затем могут быть выполнены параллельно. Для этого каждый узел потокового графа взвешивается параметром максимального времени исполнения подграфа, который начинается в этом узле и заканчивается в выходном узле. Полученный вес и называется критическим путем. На основе полученных критических путей формируется упорядоченный список узлов, которые затем динамически распределяются по процессорам в порядке убывания их весов.